The MT5C1001 employs low power, high-performance silicon-gate CMOS technology. Static design eliminates the need for external clocks or timing strobes while CMOS circuitry reduces power consumption and provides for greater reliability. For flexibility in high-speed memory applications, Micross offers chip enable (CE) and output enable (OE) capability. These e.

• High Speed: 20, 25, 35, and 45

• Battery Backup: 2V data retention

• Low power standby

• Single +5V (+10%) Power Supply

• Easy memory expansion with CE and OE options.

• All inputs and outputs are TTL compatible

• Three-state output

OPTIONS

• Timing 20ns access 25ns access 35ns access 45ns access 55ns access 70ns access

MARKING

-20 -25 -35 -45 -55

* -70

*

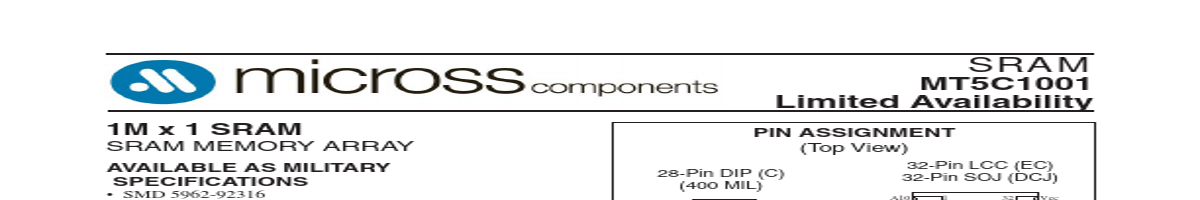

• Package(s) Ceramic DIP (400 mil) Ceramic LCC Ceramic Flatpack Ceramic SOJ

C

No. 109

EC No. 207

F

No. 303

DCJ No. 501

• Operating Temperature Ranges

Industrial (-40oC to +85oC)

IT

Military (-55oC to +125oC)

XT

• 2V data retent.

The MT5C1001 employs low power, high-performance silicon-gate CMOS technology. Static design eliminates the need for ext.

| No. | Partie # | Fabricant | Description | Fiche Technique |

|---|---|---|---|---|

| 1 | MT5C1005 |

ASI |

SRAM MEMORY ARRAY |

|

| 2 | MT5C1005 |

Micross |

256K x 4 SRAM |

|

| 3 | MT5C1005 |

Micron |

256K x 4 SRAM |

|

| 4 | MT5C1008 |

ASI |

128K x 8 SRAM WITH DUAL CHIP ENABLE AVAILABLE AS MILITARY SPECIFICATIONS |

|

| 5 | MT5C1008 |

Micron |

128K x 8 SRAM |

|

| 6 | MT5C1008LL |

Austin Semiconductor |

128K x 8 SRAM WITH DUAL CHIP ENABLE ULTRA LOW POWER |

|

| 7 | MT5C1009 |

Micross |

128K x 8 SRAM |

|

| 8 | MT5C1189 |

Micron |

128K x 9 SRAM |

|

| 9 | MT5C128K8A1 |

Micron Technology |

128K x 8 SRAM |

|

| 10 | MT5C128K8A1S13A |

Micron Technology |

1M SRAM |

|

| 11 | MT5C1601 |

Micron |

16K x 1 SRAM |

|

| 12 | MT5C1604 |

Micron |

4K x 4 SRAM |

|