The MT5C1008 SRAM employs high-speed, low power CMOS designs using a four-transistor memory cell, and are fabricated using double-layer metal, double-layer polysilicon technology. For design flexibility in high-speed memory applications, this device offers dual chip enables (CE1, CE2) and output enable (OE). These control pins can place the outputs in High-Z.

•

•

•

•

•

• High Speed: 12, 15, 20, 25, 35, 45, 55 and 70 ns Battery Backup: 2V data retention Low power standby High-performance, low-power CMOS process Single +5V (+10%) Power Supply Easy memory expansion with CE1, CE2, and OE options.

• All inputs and outputs are TTL compatible

32-Pin LCC (ECA)

4 3 2 1 32 31 30

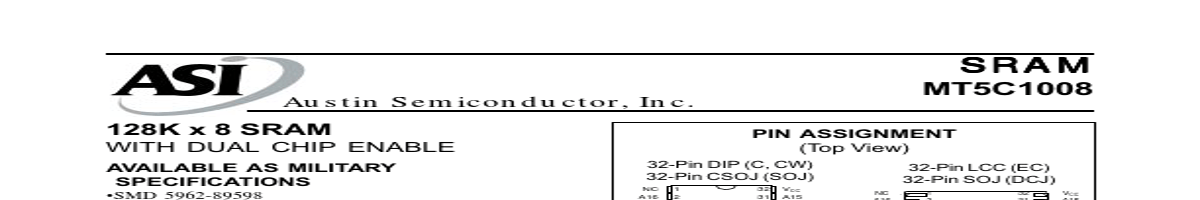

NC A16 A14 A12 A7 A6 A5 A4 A3 A2 A1 A0 DQ1 DQ2 DQ3 VSS 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 32 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 VCC A15 CE2 WE A13 A8 A9 A11 OE A10 CE DQ8 DQ7 DQ6 DQ5 DQ4

OPTIONS

• Timing 12ns access 15ns access 20ns access 25ns access 35ns access 45ns.

| No. | Partie # | Fabricant | Description | Fiche Technique |

|---|---|---|---|---|

| 1 | MT5C1001 |

ASI |

SRAM |

|

| 2 | MT5C1001 |

Micross |

1M x 1 SRAM |

|

| 3 | MT5C1001 |

Micron |

1 Meg x 1 SRAM |

|

| 4 | MT5C1005 |

ASI |

SRAM MEMORY ARRAY |

|

| 5 | MT5C1005 |

Micross |

256K x 4 SRAM |

|

| 6 | MT5C1005 |

Micron |

256K x 4 SRAM |

|

| 7 | MT5C1008LL |

Austin Semiconductor |

128K x 8 SRAM WITH DUAL CHIP ENABLE ULTRA LOW POWER |

|

| 8 | MT5C1009 |

Micross |

128K x 8 SRAM |

|

| 9 | MT5C1189 |

Micron |

128K x 9 SRAM |

|

| 10 | MT5C128K8A1 |

Micron Technology |

128K x 8 SRAM |

|

| 11 | MT5C128K8A1S13A |

Micron Technology |

1M SRAM |

|

| 12 | MT5C1601 |

Micron |

16K x 1 SRAM |

|