The 13-bit-to-26-bit ICSSSTVF16859 is a universal bus driver designed for 2.3V to 2.7V VDD operation and SSTL_2 I/O levels, except for the LVCMOS RESET# input. Data flow from D to Q is controlled by the differential clock (CLK/CLK#) and a control signal (RESET#). The positive edge of CLK is used to trigger the data flow and CLK# is used to maintain sufficien.

• Differential clock signals

• Meets SSTL_2 signal data

• Supports SSTL_2 class I specifications on outputs

• Low-voltage operation - VDD = 2.3V to 2.7V

• Available in 64 pin TSSOP and 56 pin MLF packages

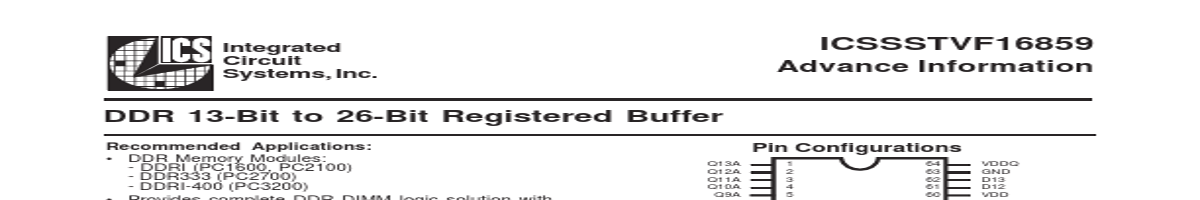

Pin Configurations

Q13A Q12A Q11A Q10A Q9A VDDQ GND Q8A Q7A Q6A Q5A Q4A Q3A Q2A GND Q1A Q13B VDDQ Q12B Q11B Q10B Q9B Q8B Q7B Q6B GND VDDQ Q5B Q4B Q3B Q2B Q1B 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 64 63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 VDDQ GND D13 D12 VDD VDDQ GND D11 D10 D9 GND D8 D7 R.

| No. | Partie # | Fabricant | Description | Fiche Technique |

|---|---|---|---|---|

| 1 | ICSSSTVF16857 |

Renesas |

DDR 14-Bit Registered Buffer |

|

| 2 | ICSSSTV16857 |

Integrated Circuit Systems |

DDR 14-Bit Registered Buffer |

|

| 3 | ICSSSTV16859 |

Integrated Circuit Systems |

DDR 13-Bit to 26-Bit Registered Buffer |

|

| 4 | ICSSSTV32852 |

Integrated Circuit Systems |

DDR 24-Bit to 48-Bit Registered Buffer |

|

| 5 | ICSSSTVA16857 |

Integrated Circuit Systems |

DDR 14-Bit Registered Buffer |

|

| 6 | ICSSSTVA16859B |

Integrated Circuit Systems |

DDR 13-Bit to 26-Bit Registered Buffer |

|

| 7 | ICSSSTVA16859C |

Renesas |

DDR 13-Bit to 26-Bit Registered Buffer |

|

| 8 | ICSSSTVA16859C |

IDT |

DDR 13-Bit to 26-Bit Registered Buffer |

|

| 9 | ICSSSTU32864 |

ICS |

25-Bit Configurable Registered Buffer |

|

| 10 | ICSSSTU32866 |

Integrated Circuit System |

25-Bit Configurable Registered Buffer |

|

| 11 | ICSSSTUA32S869B |

ICS |

14-Bit Configurable Registered Buffer |

|

| 12 | ICSSSTUAF32865A |

IDT |

25-BIT CONFIGURABLE REGISTERED BUFFER |

|