19.20 20.00 Max 16 9 7.40 Max 6.30 Unit: mm 1 1.3 1.11 Max 8 0.51 Min 2.54 Min 5.06 Max 7.62 2.54 ± 0.25 0.48 ± 0.10 0.25 – 0.05 0° – 15° Hitachi Code JEDEC EIAJ Weight (reference value) + 0.13 DP-16 Conforms Conforms 1.07 g Unit: mm 10.06 10.5 Max 16 9 5.5 1 *0.22 ± 0.05 0.20 ± 0.04 8 0.80 Max 2.20 Max 0.20 7.80 + – 0.30 1.15 0° – 8° 0.70 ±.

s or any third party’s patent, copyright, trademark, or other intellectual property rights for information contained in this document. Hitachi bears no responsibility for problems that may arise with third party’s rights, including intellectual property rights, in connection with use of the information contained in this document. 2. Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use. 3. Hitachi makes every attempt to ensure that its products are of high q.

| No. | Partie # | Fabricant | Description | Fiche Technique |

|---|---|---|---|---|

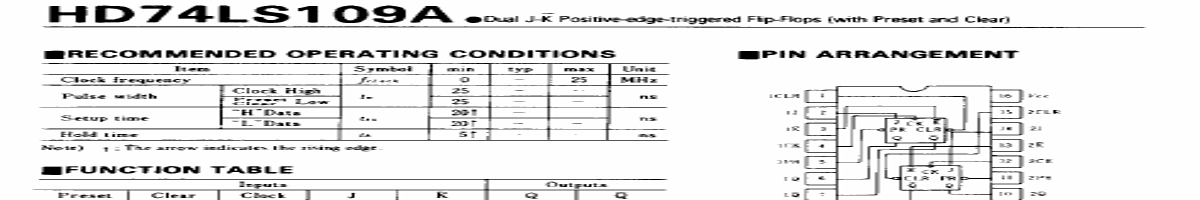

| 1 | HD74LS109 |

Hitachi Semiconductor |

Dual J-K Positive-edge-triggered Flip-Flops |

|

| 2 | HD74LS10 |

Hitachi Semiconductor |

Triple 3-input Positive NAND Gates |

|

| 3 | HD74LS10 |

Renesas |

Triple 3-Input Positive NAND Gates |

|

| 4 | HD74LS107A |

Hitachi Semiconductor |

Dual J-K Negative-edge-triggered Flip-Flops |

|

| 5 | HD74LS107A |

Renesas |

Dual J-K Negative-edge-triggered Flip-Flops |

|

| 6 | HD74LS107AP |

Renesas |

Dual J-K Negative-edge-triggered Flip-Flops |

|

| 7 | HD74LS10P |

Renesas |

Triple 3-Input Positive NAND Gates |

|

| 8 | HD74LS11 |

Hitachi Semiconductor |

Triple 3-input Positive AND Gates |

|

| 9 | HD74LS11 |

Renesas |

Triple 3-input Positive AND Gates |

|

| 10 | HD74LS112 |

Hitachi Semiconductor |

Dual J-K Negative-edge-triggered Flip-Flops |

|

| 11 | HD74LS112 |

Renesas |

Dual J-K Negative-edge-triggered Flip-Flops |

|

| 12 | HD74LS112P |

Renesas |

Dual J-K Negative-edge-triggered Flip-Flops |

|