2Mega x 32 SDRAM EM638325 Table 1. Pin Details of EM638325 Symbol Type Description CLK Input Clock: CLK is driven by the system clock. All SDRAM input signals are sampled on the positive edge of CLK. CLK also increments the internal burst counter and controls the output registers. Input Clock Enable: CKE activates(HIGH) and deactivates(LOW) the CLK signa.

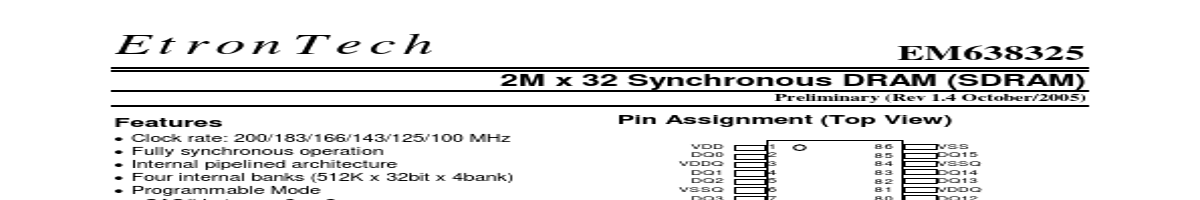

Clock rate: 200/183/166/143/125/100 MHz Fully synchronous operation Internal pipelined architecture Four internal banks (512K x 32bit x 4bank) Programmable Mode - CAS# Latency: 2 or 3 - Burst Length: 1, 2, 4, 8, or full page - Burst Type: interleaved or linear burst - Burst-Read-Single-Write

• Burst stop function

• Individual byte controlled by DQM0-3

• Auto Refresh and Self Refresh

• 4096 refresh cycles/64ms

• Single +3.3V ± 0.3V power supply

• Interface: LVTTL

• Package: 400 x 875 mil, 86 Pin TSOP II, 0.50mm pin pitch Lead Free Package available

•

•

•

•

•

•

EM638325

2M x 32 Synchronous DRAM.

| No. | Partie # | Fabricant | Description | Fiche Technique |

|---|---|---|---|---|

| 1 | EM638165 |

Etron Technology |

4M x 16 bit Synchronous DRAM |

|

| 2 | EM638165TS |

Etron Technology |

4M x 16 bit Synchronous DRAM |

|

| 3 | EM6352 |

EM Microelectronic - MARIN SA |

Voltage Detecto |

|

| 4 | EM6353 |

EM Microelectronic - MARIN SA |

Reset Circuit |

|

| 5 | EM6354 |

EM Microelectronic - MARIN SA |

Reset Circuit |

|

| 6 | EM636165 |

Etron |

1M x 16 Synchronous DRAM |

|

| 7 | EM636165-XXI |

Etron Technology |

1Mega x 16 Synchronous DRAM |

|

| 8 | EM636327 |

Etron Technology Inc. |

512K x 32 High Speed Synchronous Graphics DRAM(SGRAM) |

|

| 9 | EM637327 |

Etron Technology Inc. |

1Mega x 32 SGRAM |

|

| 10 | EM639165 |

Etron Technology Inc. |

8Mega x 16bits SDRAM |

|

| 11 | EM639165TS |

Etron Technology |

8M x 16 bit Synchronous DRAM |

|

| 12 | EM639325 |

Etron Technology |

4M x 32 bit Synchronous DRAM |

|