1Mega x 32 SGRAM EM637327 Table 1. Pin Details of EM637327 Symbol Type Description CLK Input Clock: CLK is driven by the system clock. All SGRAM input signals are sampled on the positive edge of CLK. CLK also increments the internal burst counter and controls the output registers. Input Clock Enable: CKE activates(HIGH) and deactivates(LOW) the CLK signa.

•

•

•

•

•

•

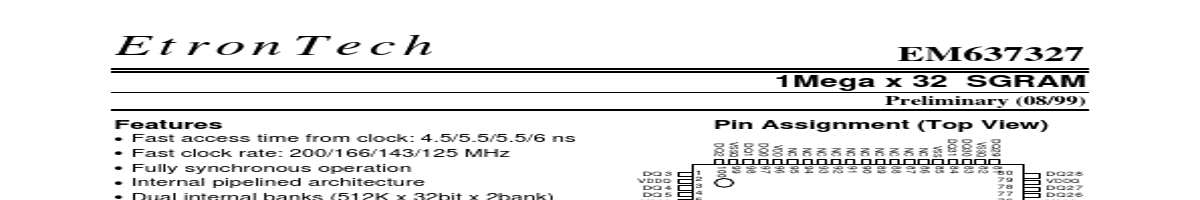

EM637327

1Mega x 32 SGRAM

Preliminary (08/99)

Pin Assignment (Top View)

DQ29 VSSQ DQ30 DQ31 VSS NC NC NC NC NC NC NC NC NC NC V DD DQ0 DQ1 VSSQ DQ2

•

•

•

•

•

•

•

•

Fast access time from clock: 4.5/5.5/5.5/6 ns Fast clock rate: 200/166/143/125 MHz Fully synchronous operation Internal pipelined architecture Dual internal banks (512K x 32bit x 2bank) Programmable Mode - CAS# Latency: 1, 2, or 3 - Burst Length: 1, 2, 4, 8, or full page - Burst Type: interleaved or linear burst - Burst-Read-Single-Write - Load Color or Mask register Burst stop function Individual byte controlled by .

| No. | Partie # | Fabricant | Description | Fiche Technique |

|---|---|---|---|---|

| 1 | EM6352 |

EM Microelectronic - MARIN SA |

Voltage Detecto |

|

| 2 | EM6353 |

EM Microelectronic - MARIN SA |

Reset Circuit |

|

| 3 | EM6354 |

EM Microelectronic - MARIN SA |

Reset Circuit |

|

| 4 | EM636165 |

Etron |

1M x 16 Synchronous DRAM |

|

| 5 | EM636165-XXI |

Etron Technology |

1Mega x 16 Synchronous DRAM |

|

| 6 | EM636327 |

Etron Technology Inc. |

512K x 32 High Speed Synchronous Graphics DRAM(SGRAM) |

|

| 7 | EM638165 |

Etron Technology |

4M x 16 bit Synchronous DRAM |

|

| 8 | EM638165TS |

Etron Technology |

4M x 16 bit Synchronous DRAM |

|

| 9 | EM638325 |

Etron Technology |

2M x 32 Synchronous DRAM |

|

| 10 | EM639165 |

Etron Technology Inc. |

8Mega x 16bits SDRAM |

|

| 11 | EM639165TS |

Etron Technology |

8M x 16 bit Synchronous DRAM |

|

| 12 | EM639325 |

Etron Technology |

4M x 32 bit Synchronous DRAM |

|