The PLL102-03 is a high performance, low skew, low jitter zero delay buffer designed to distribute high speed clocks and is available in an 8-pin SOIC package. It has four outputs that are synchronized with the input. The synchronization is established via CLKOUT feed back to the input of the PLL. Since the skew between the input and output is less than ± 35.

Frequency range 75 ~ 180MHz. Internal phase locked loop will allow spread spectrum modulation on reference clock to pass to the outputs (up to 100kHz SST modulation).

• Zero input - output delay.

• Less than 700 ps device - device skew.

• Less than 250 ps skew between outputs. www.DataSheet4U.com

• Less than 150 ps cycle - cycle jitter.

• Output Enable function tri-state outputs.

• 3.3V operation.

• Available in 8-Pin 150mil SOIC GREEN package.

•

•

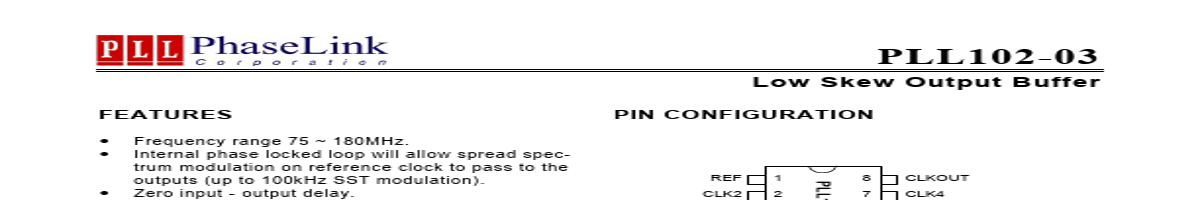

PIN CONFIGURATION

REF CLK2 CLK1 GND

1 2 3 4

8 7 6 5

CLKOUT CLK4 VDD CLK3

PLL102-03

Remark

If REF clock is stopped for more than 10us after i.

| No. | Partie # | Fabricant | Description | Fiche Technique |

|---|---|---|---|---|

| 1 | PLL102-04 |

PhaseLink Corporation |

Low Skew Output Buffer |

|

| 2 | PLL102-05 |

PhaseLink Corporation |

Low Skew Output Buffer |

|

| 3 | PLL102-10 |

PhaseLink Corporation |

Low Skew Output Buffer |

|

| 4 | PLL102-108 |

PhaseLink Corporation |

Programmable DDR Zero Delay Clock Driver |

|

| 5 | PLL102-109 |

PhaseLink Corporation |

Programmable DDR Zero Delay Clock Driver |

|

| 6 | PLL102-15 |

PhaseLink Corporation |

Low Skew Output Buffer |

|

| 7 | PLL1000A |

Z-Communications |

PHASE LOCKED LOOP |

|

| 8 | PLL103-01 |

PhaseLink Corporation |

Low Skew Buffer |

|

| 9 | PLL103-02 |

PhaseLink Corporation |

DDR SDRAM Buffer |

|

| 10 | PLL103-03 |

PhaseLink Corporation |

DDR SDRAM Buffer |

|

| 11 | PLL103-04 |

PhaseLink Corporation |

1-to-4 Clock Distribution Buffer |

|

| 12 | PLL103-05 |

PhaseLink Corporation |

1-to-5 Clock Distribution Buffer |

|