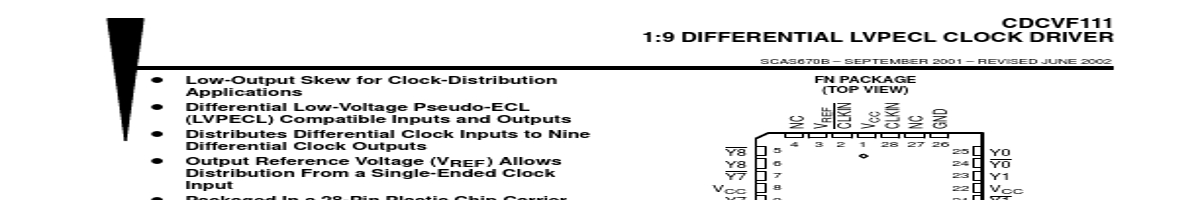

The differential LVPECL clock-driver circuit distributes one pair of differential LVPECL clock inputs (CLKIN, CLKIN) to nine pairs of differential clock (Y, Y) outputs with minimum skew for clock distribution. It is specifically designed for driving 50-Ω transmission lines. FN PACKAGE (TOP VIEW) NC VREF CLKIN VCC CLKIN NC GND Y8 Y8 Y7 VCC Y7 Y6 Y6 4 3 2 .

e CLKIN input for a single-ended CLKIN input. The CDCVF111 is characterized for operation from

–40°C to 85°C.

FUNCTION TABLE

INPUTS

OUTPUTS

CLKIN CLKIN Yn Yn

X

X

L

H

L

H

L

H

H

L

H

L

L

VREF

L

H

H

VREF H

L

VREF

L

H

L

VREF

H

L

H

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of T.

| No. | Partie # | Fabricant | Description | Fiche Technique |

|---|---|---|---|---|

| 1 | CDCVF2310 |

Texas Instruments |

2.5-V to 3.3-V High-Performance Clock Buffer |

|

| 2 | CDCVF2310-EP |

Texas Instruments |

2.5-V TO 3.3-V HIGH-PERFORMANCE CLOCK BUFFER |

|

| 3 | CDCVF2505 |

Texas Instruments |

3.3-V Clock Phase-Lock Loop Clock Driver |

|

| 4 | CDCVF2505-Q1 |

Texas Instruments |

3.3-V CLOCK PHASE-LOCKED LOOP CLOCK DRIVER |

|

| 5 | CDCVF25081 |

Texas Instruments |

3.3-V Phased-Lock Loop Clock Driver |

|

| 6 | CDCVF25084 |

Texas Instruments |

3.3-V 1:8 ZERO DELAY x4 CLOCK MULTIPLIER |

|

| 7 | CDCVF2509 |

Texas Instruments |

3.3-V PHASE-LOCK LOOP CLOCK DRIVER |

|

| 8 | CDCVF2509A |

Texas Instruments |

3.3-V PHASE-LOCK LOOP CLOCK DRIVER |

|

| 9 | CDCVF2510 |

Texas Instruments |

3.3-V PHASE-LOCK LOOP CLOCK DRIVER |

|

| 10 | CDCVF2510A |

Texas Instruments |

3.3-V PHASE-LOCK LOOP CLOCK DRIVER |

|

| 11 | CDCVF310 |

Texas Instruments |

2.5-V TO 3.3-V HIGH-PERFORMANCE CLOCK BUFFER |

|

| 12 | CDCVF855 |

Texas Instruments |

2.5-V PHASE-LOCKED-LOOP CLOCK DRIVER |

|