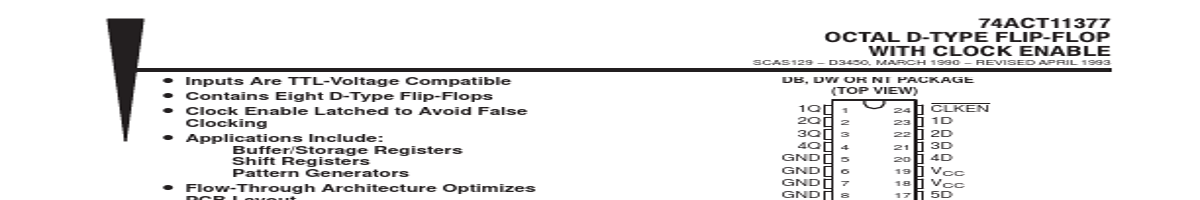

These circuits are positive-edge-triggered D-type flip-flops with a clock enable input. Information at the D inputs meeting the setup time requirements is transferred to the Q outputs on the positive-going edge of the clock pulse if CLKEN is low. Clock triggering occurs at a particular voltage level and is not directly related to the transition time of the p.

uirements is transferred to the Q outputs on the positive-going edge of the clock pulse if CLKEN is low. Clock triggering occurs at a particular voltage level and is not directly related to the transition time of the positive-going pulse. When the clock input is at either the high or low level, the D input signal has no effect at the output. The circuits are designed to prevent false clocking by transitions at the CLKEN input. The 74ACT11377 is characterized for operation from − 40°C to 85°C. FUNCTION TABLE (each flip-flop) INPUTS CLKEN CLK D OUTPUT Q H X X Q0 L ↑H H L ↑L L X L X Q0 .

| No. | Partie # | Fabricant | Description | Fiche Technique |

|---|---|---|---|---|

| 1 | 74ACT11373 |

Texas Instruments |

OCTAL TRANSPARENT D-TYPE LATCH |

|

| 2 | 74ACT11374 |

Texas Instruments |

OCTAL EDGE-TRIGGERED D-TYPE FLIP-FLOP |

|

| 3 | 74ACT11378 |

Texas Instruments |

HEX D-TYPE FLIP FLOP |

|

| 4 | 74ACT11379 |

Texas Instruments |

QUAD D-TYPE FLIP FLOP |

|

| 5 | 74ACT11352 |

Texas Instruments |

DUAL 4-LINE TO 1-LINE DATA SELECTOR/MULTIPLEXER |

|

| 6 | 74ACT11353 |

Texas Instruments |

Dual 1-of-4 Data Selectors/Multiplexers |

|

| 7 | 74ACT11 |

STMicroelectronics |

TRIPLE 3-INPUT AND GATE |

|

| 8 | 74ACT11000 |

Texas Instruments |

QUADRUPLE 2-INPUT POSITIVE-NAND GATES |

|

| 9 | 74ACT11002 |

Texas Instruments |

QUADRUPLE 2-INPUT POSITIVE-NOR GATES |

|

| 10 | 74ACT11004 |

Texas Instruments |

HEX INVERTER |

|

| 11 | 74ACT11008 |

Texas Instruments |

QUADRUPLE 2-INPUT POSITIVE-AND GATE |

|

| 12 | 74ACT11010 |

Texas Instruments |

Triple 3-Input Positive-NAND Gates |

|