|

Part Number

|

HEF40195B |

|

Manufacturer

|

NXP (https://www.nxp.com/) |

|

Description

|

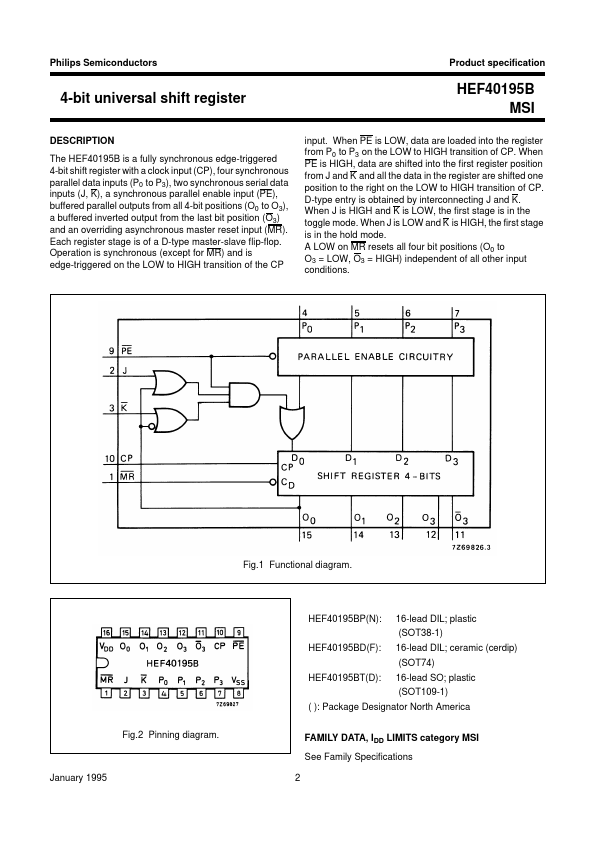

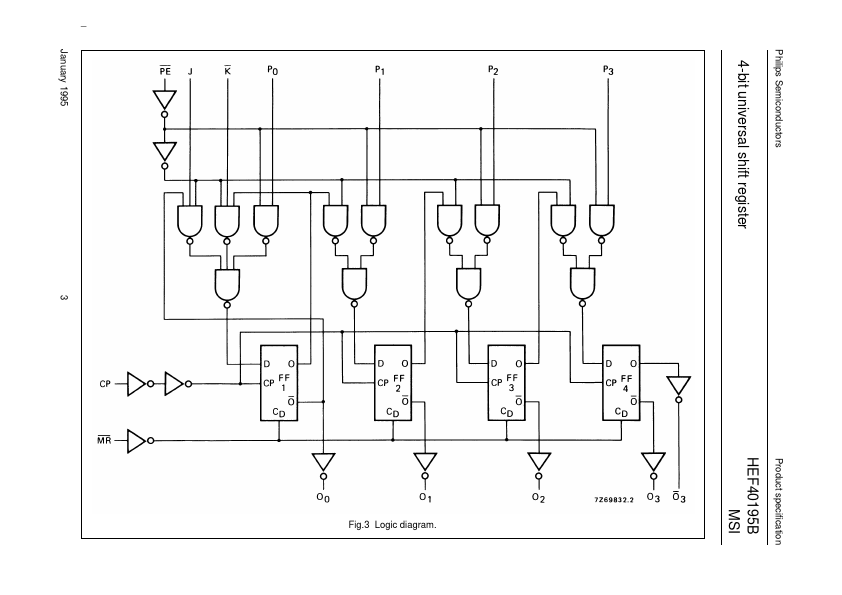

The HEF40195B is a fully synchronous edge-triggered 4-bit shift register with a clock input (CP), four synchronous parallel data inputs (P0 to P3), two synchronous serial data inputs (J, K), a synchro...

|

|

Features

|

195B MSI

input. When PE is LOW, data are loaded into the register from P0 to P3 on the LOW to HIGH transition of CP. When PE is HIGH, data are shifted into the first register position from J and K and all the data in the register are shifted one position to the right on the LOW to HIGH transition of CP. D-type entry is obtained by interconnecting J and K. When J is HIGH and K is LOW, the first stage is in the toggle mode. When J is LOW and K is HIGH, the first stage is in the hold mode. A LOW on MR resets all four bit positions (O0 to O3 = LOW, O3 = HIGH) independent of all other input conditi...

|

|

Document

|

HEF40195B Data Sheet HEF40195B Data Sheet

PDF 77.78KB |