Recherchez avec le numéro de pièce ainsi que le fabricant ou la description

PLL102-15 |

| Part Number | PLL102-15 |

| Manufacturer | PhaseLink Corporation |

| Description | The PLL102 -15 is a high performance, low skew, low jitter zero delay buffer designed to di stribute high speed clocks and is available in 8 -pin SOIC or TSSOP package. It has four outputs that are s... |

| Features |

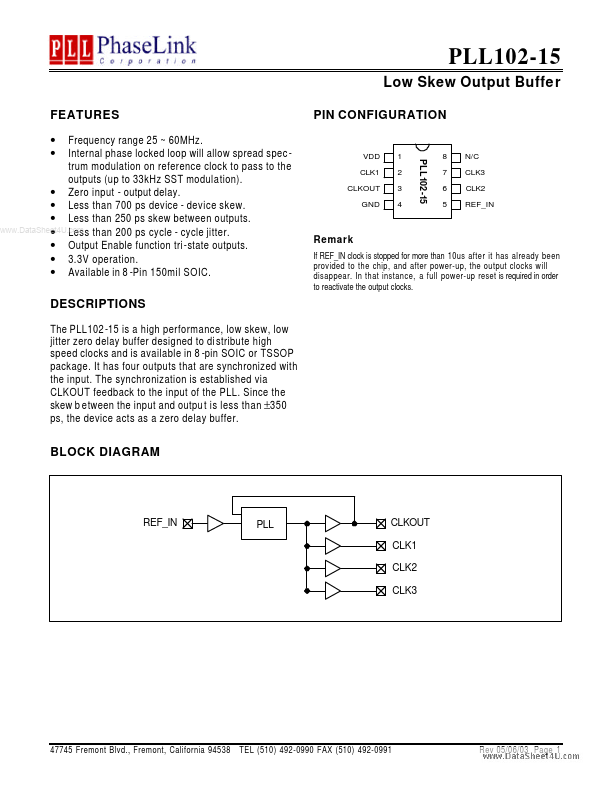

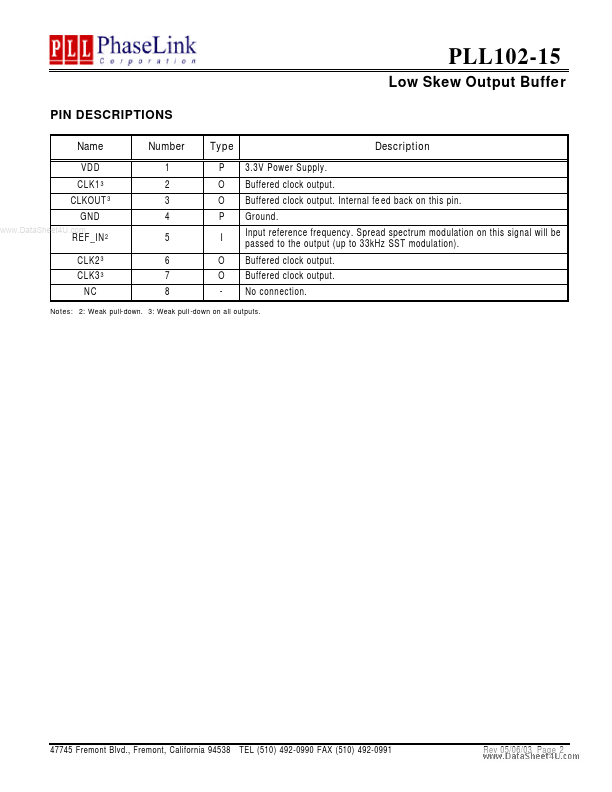

Frequency range 25 ~ 60MHz. Internal phase locked loop will allow spread spec trum modulation on reference clock to pass to the outputs (up to 33kHz SST modulation). • Zero input - output delay. • Less than 700 ps device - device skew. • Less than 250 ps skew between outputs. www.DataSheet4U.com • Less than 200 ps cycle - cycle jitter. • Output Enable function tri -state outputs. • 3.3V operation. • Available in 8 -Pin 150mil SOIC. • • PIN CONFIGURATION VDD CLK1 CLKOUT GND 1 2 3 4 8 7 6 5 N/C CLK3 CLK2 REF_IN PLL102-15 Remark If REF_IN clock is stopped for more than 10us after it has al... |

| Document |

PDF 141.06KB |

| Distributor | Stock | Price | Buy |

|---|

| No. | Partie # | Fabricant | Description | Fiche Technique |

|---|---|---|---|---|

| 1 | PLL102-10 |

PhaseLink Corporation |

Low Skew Output Buffer |

|

| 2 | PLL102-108 |

PhaseLink Corporation |

Programmable DDR Zero Delay Clock Driver |

|

| 3 | PLL102-109 |

PhaseLink Corporation |

Programmable DDR Zero Delay Clock Driver |

|

| 4 | PLL102-03 |

PhaseLink Corporation |

Low Skew Output Buffer |

|

| 5 | PLL102-04 |

PhaseLink Corporation |

Low Skew Output Buffer |

|