Recherchez avec le numéro de pièce ainsi que le fabricant ou la description

PLL102-108 |

| Part Number | PLL102-108 |

| Manufacturer | PhaseLink Corporation |

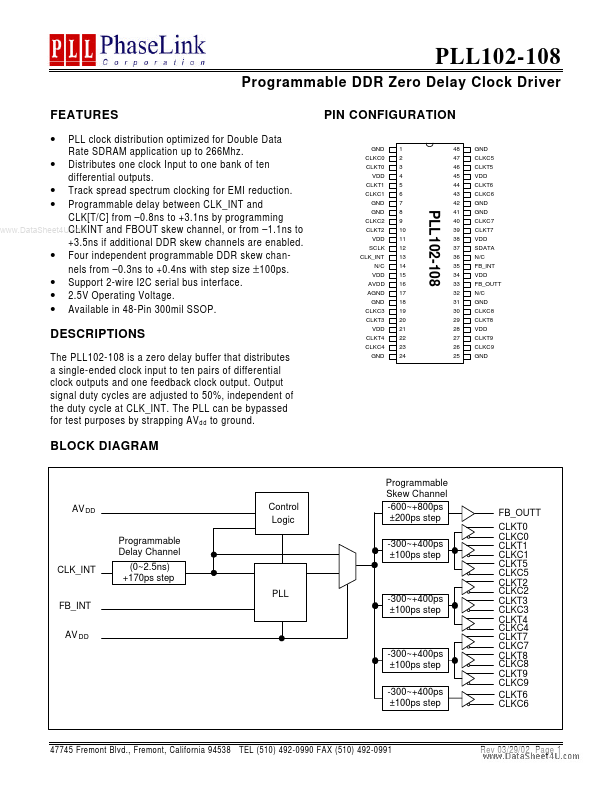

| Description | The PLL102-108 is a zero delay buffer that distributes a single-ended clock input to ten pairs of differential clock outputs and one feedback clock output. Output signal duty cycles are adjusted to 5... |

| Features |

PLL clock distribution optimized for Double Data Rate SDRAM application up to 266Mhz. • Distributes one clock Input to one bank of ten differential outputs. • Track spread spectrum clocking for EMI reduction. • Programmable delay between CLK_INT and CLK[T/C] from –0.8ns to +3.1ns by programming www.DataSheet4U.com CLKINT and FBOUT skew channel, or from –1.1ns to +3.5ns if additional DDR skew channels are enabled. • Four independent programmable DDR skew channels from –0.3ns to +0.4ns with step size ± 100ps. • Support 2-wire I2C serial bus interface. • 2.5V Operating Voltage. • Available in 48-... |

| Document |

PDF 198.33KB |

| Distributor | Stock | Price | Buy |

|---|

| No. | Partie # | Fabricant | Description | Fiche Technique |

|---|---|---|---|---|

| 1 | PLL102-10 |

PhaseLink Corporation |

Low Skew Output Buffer |

|

| 2 | PLL102-109 |

PhaseLink Corporation |

Programmable DDR Zero Delay Clock Driver |

|

| 3 | PLL102-15 |

PhaseLink Corporation |

Low Skew Output Buffer |

|

| 4 | PLL102-03 |

PhaseLink Corporation |

Low Skew Output Buffer |

|

| 5 | PLL102-04 |

PhaseLink Corporation |

Low Skew Output Buffer |

|