Recherchez avec le numéro de pièce ainsi que le fabricant ou la description

ICSSSTUB32872A |

| Part Number | ICSSSTUB32872A |

| Manufacturer | ICS |

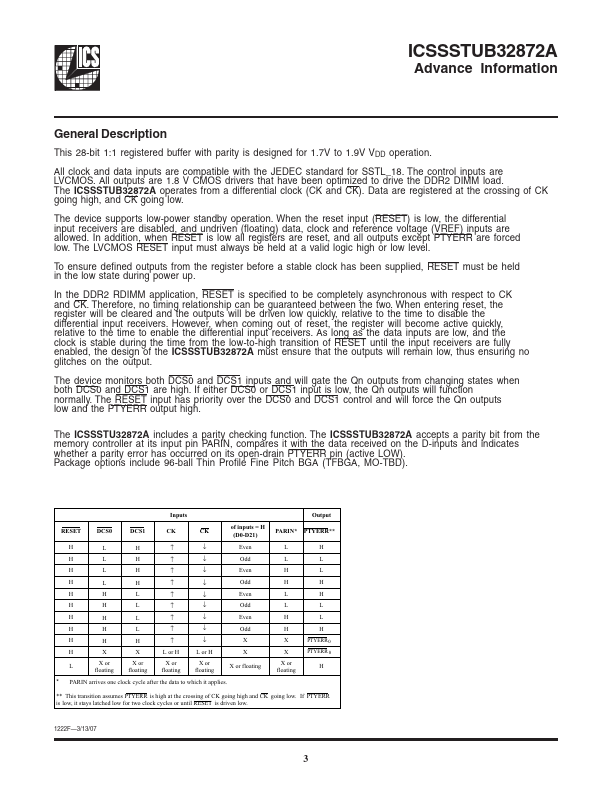

| Description | This 28-bit 1:1 registered buffer with parity is designed for 1.7V to 1.9V VDD operation. All clock and data inputs are compatible with the JEDEC standard for SSTL_18. The control inputs are LVCMOS. A... |

| Features |

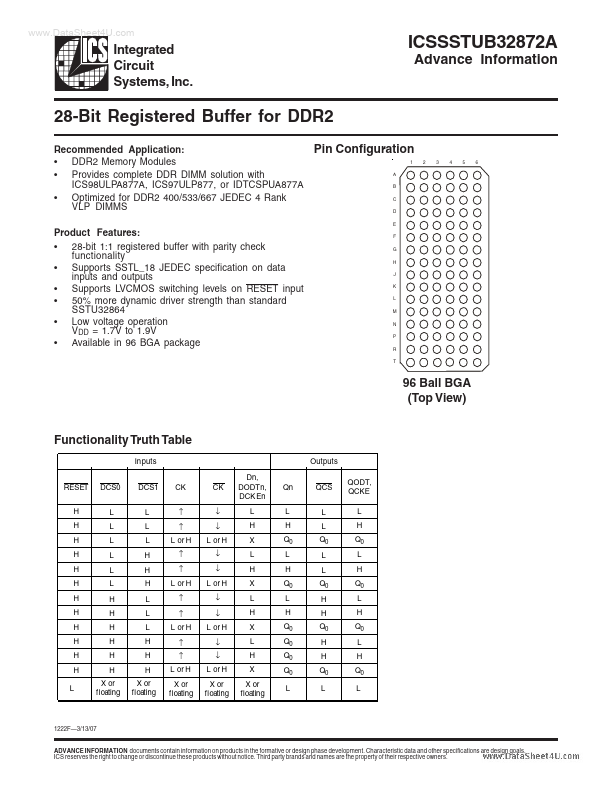

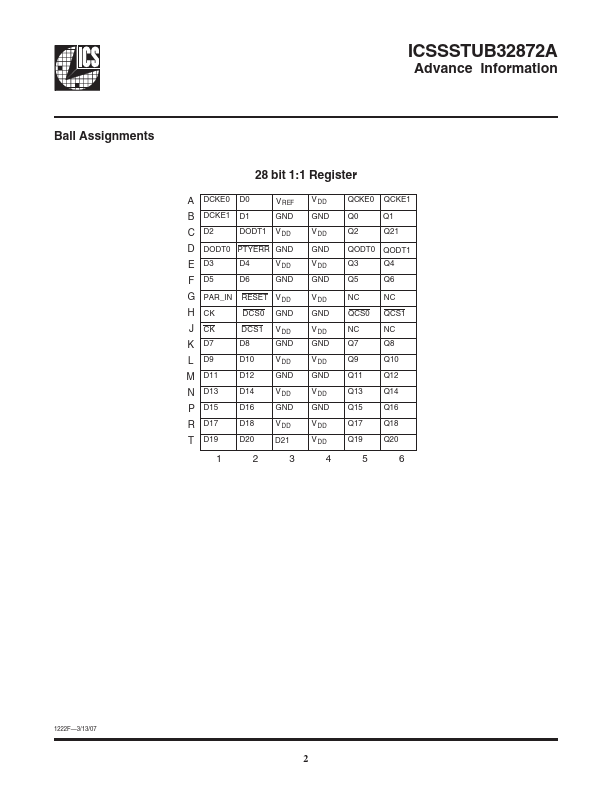

• 28-bit 1:1 registered buffer with parity check functionality • Supports SSTL_18 JEDEC specification on data inputs and outputs • Supports LVCMOS switching levels on RESET input • 50% more dynamic driver strength than standard SSTU32864 • Low voltage operation VDD = 1.7V to 1.9V • Available in 96 BGA package Pin Configuration 1 A B C D E F G H J K L M N P R T 2 3 4 5 6 96 Ball BGA (Top View) Functionality Truth Table In puts RESET H H H H H H H H H H H H L DCS0 L L L L L L H H H H H H X or floating DCS1 L L L H H H L L L H H H X or floating CK ↑ ↑ L or H ↑ ↑ L or H ↑ ↑ L or H ↑ ↑ L or H X... |

| Document |

PDF 238.50KB |

| Distributor | Stock | Price | Buy |

|---|

| No. | Partie # | Fabricant | Description | Fiche Technique |

|---|---|---|---|---|

| 1 | ICSSSTUB32871A |

ICS |

27-Bit Registered Buffer |

|

| 2 | ICSSSTUB32864A |

ICS |

25-Bit Configurable Registered Buffer |

|

| 3 | ICSSSTUB32866B |

ICS |

25-Bit Configurable Registered Buffer |

|

| 4 | ICSSSTUBF32866A |

ICS |

25-Bit Configurable Registered Buffer |

|

| 5 | ICSSSTU32864 |

ICS |

25-Bit Configurable Registered Buffer |

|