Recherchez avec le numéro de pièce ainsi que le fabricant ou la description

P5010 |

| Part Number | P5010 |

| Manufacturer | NXP (https://www.nxp.com/) |

| Description | Freescale Semiconductor Data Sheet: Technical Data QorIQ P5020/P5010 Data Sheet Document Number: P5020 Rev. 1, 03/2015 P5020/P5010 FC-PBGA–1295 37.5 mm × 37.5 mm The P5020 and P5010 QorIQ integrated... |

| Features |

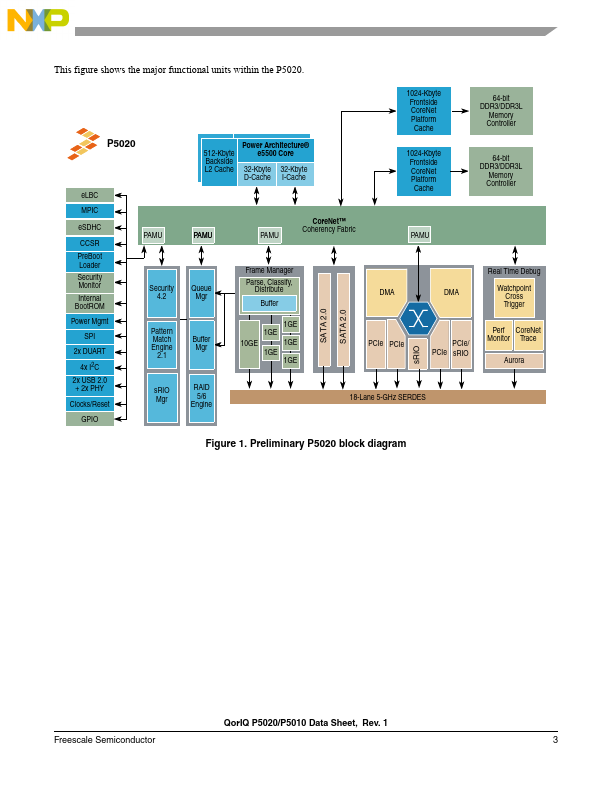

• Two e5500 Power Architecture cores (one on the P5010) – Each core has a backside 512-Kbyte L2 Cache with ECC – Three levels of instructions: User, Supervisor, and Hypervisor – Independent boot and reset – Secure boot capability • CoreNet fabric supporting coherent and non-coherent transactions amongst CoreNet endpoints • 2-Mbyte CoreNet platform cache with ECC (one on the P5010) • One 10-Gigabit Ethernet (XAUI) controller • Five 1-Gigabit Ethernet controllers – 1 Gb/s SGMII, 2.5 Gb/s SGMII and RGMII interfaces • Two 64-bit DDR3/3L SDRAM memory controllers with ECC (one on the P5010) • Multi... |

| Document |

PDF 3.19MB |

| Distributor | Stock | Price | Buy |

|---|