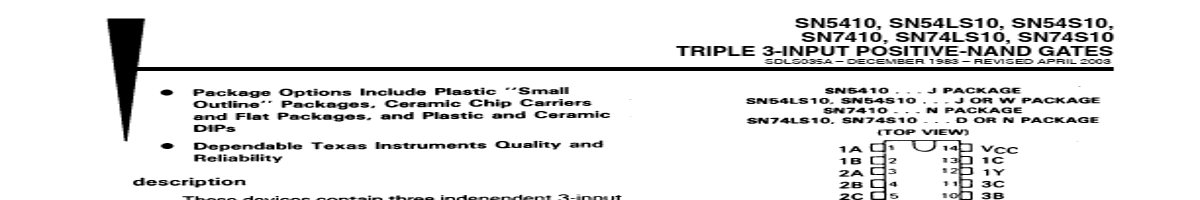

SN5410, SN54LS10, SN54S10, SN7410, SN74LS10, SN74S10 TRIPLE 3-INPUT POSITIVE-NAND GATES SDLS035A – DECEMBER 1983 – REVISED APRIL 2003 PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all paramet.

CEMBER 1983

– REVISED MARCH 1988

•POST OFFICE BOX 655303 DALLAS, TEXAS 75265

5

PACKAGE OPTION ADDENDUM

www.ti.com

24-Aug-2018

PACKAGING INFORMATION

Orderable Device JM38510/07005BCA

Status Package Type Package Pins Package

(1)

Drawing

Qty

ACTIVE

CDIP

J 14 1

Eco Plan

(2)

TBD

JM38510/07005BDA

ACTIVE

CFP

W 14 1

TBD

JM38510/30005B2A

ACTIVE

LCCC

FK 20

1

TBD

JM38510/30005BCA

ACTIVE

CDIP

J 14 1

TBD

JM38510/30005BDA

ACTIVE

CFP

W 14 1

TBD

JM38510/30005SDA

ACTIVE

CFP

W 14 25

TBD

M38510/07005BCA

ACTIVE

CDIP

J 14 1

TBD

M38510/07005BDA

ACTIVE

CFP

W 14 1

TB.

SN74LS10 TRIPLE 3-INPUT NAND GATE VCC 14 13 12 11 10 9 8 1234567 GND Symbol VCC Supply Voltage Parameter TA Op.

| No. | Partie # | Fabricant | Description | Fiche Technique |

|---|---|---|---|---|

| 1 | SN74LS107A |

Motorola |

DUAL JK NEGATIVE EDGE-TRIGGERED FLIP-FLOP |

|

| 2 | SN74LS107A |

Texas Instruments |

DUAL J-K FLIP-FLOPS |

|

| 3 | SN74LS109 |

ON Semiconductor |

LOW POWER SCHOTTKY |

|

| 4 | SN74LS109A |

ON Semiconductor |

Dual JK Positive Edge-Triggered Flip-Flop |

|

| 5 | SN74LS109A |

Motorola |

DUAL JK POSITIVE EDGE-TRIGGERED FLIP-FLOP |

|

| 6 | SN74LS109A |

Texas Instruments |

Dual J-K Positive-Edge-Triggered Flip-Flops |

|

| 7 | SN74LS11 |

Motorola |

TRIPLE 3-INPUT AND GATE |

|

| 8 | SN74LS11 |

Texas Instruments |

TRIPLE 3-INPUT POSITIVE-AND GATES |

|

| 9 | SN74LS112A |

Texas Instruments |

Dual J-K Negative-Edge-Triggered Flip-Flops |

|

| 10 | SN74LS112A |

Motorola |

DUAL JK NEGATIVE EDGE-TRIGGERED FLIP-FLOP |

|

| 11 | SN74LS113A |

Motorola |

DUAL JK NEGATIVE EDGE-TRIGGERED FLIP-FLOP |

|

| 12 | SN74LS114A |

Motorola |

DUAL JK NEGATIVE EDGE-TRIGGERED FLIP-FLOP |

|