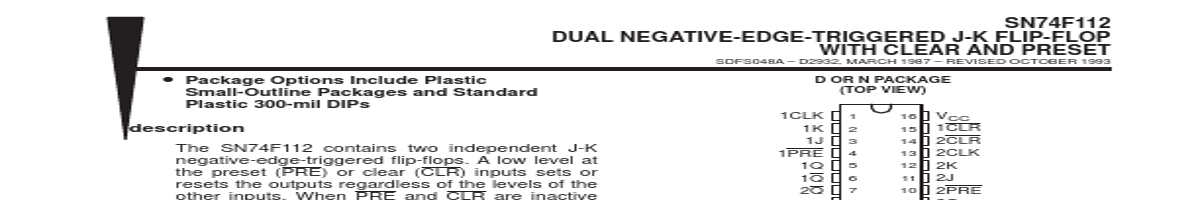

The SN74F112 contains two independent J-K negative-edge-triggered flip-flops. A low level at the preset (PRE) or clear (CLR) inputs sets or resets the outputs regardless of the levels of the other inputs. When PRE and CLR are inactive (high), data at the J and K inputs meeting the setup time requirements is transferred to the outputs on the negative-going ed.

14 2CLR 13 2CLK 12 2K 11 2J 10 2PRE 9 2Q The SN74F112 is characterized for operation from 0°C to 70°C. FUNCTION TABLE INPUTS OUTPUTS PRE CLR CLK J K Q Q L H X X X H L H L X X X L H L L X X X H† H† H H ↓ L L Q0 Q0 H H ↓ H L H L H H ↓ L H L H H H ↓ H H Toggle H H H X X Q0 Q0 † The output levels in this configuration are not guaranteed to meet the minimum levels for VOH. Furthermore, this configuration is nonstable; that is, it will not persist when either PRE or CLR returns to its inactive (high) level. PRODUCTION DATA information.

| No. | Partie # | Fabricant | Description | Fiche Technique |

|---|---|---|---|---|

| 1 | SN74F11 |

Texas Instruments |

Triple 3-Input AND Gate |

|

| 2 | SN74F10 |

Texas Instruments |

TRIPLE 3-INPUT POSITIVE-NAND GATE |

|

| 3 | SN74F1016 |

Texas Instruments |

16-Bit Schottky Barrier Diode RC Bus-Termination Array |

|

| 4 | SN74F1056 |

Texas Instruments |

8-BIT SCHOTTKY BARRIER DIODE BUS-TERMINATION ARRAY |

|

| 5 | SN74F109 |

Texas Instruments |

DUAL J-K POSITIVE-EDGE-TRIGGERED FLIP-FLOP |

|

| 6 | SN74F125 |

Texas Instruments |

QUADRUPLE BUS BUFFER GATE |

|

| 7 | SN74F126 |

Texas Instruments |

QUADRUPLE BUS BUFFER GATE |

|

| 8 | SN74F138 |

Texas Instruments |

3-LINE TO 8-LINE DECODERS/DEMULTIPLEXERS |

|

| 9 | SN74F151B |

Texas Instruments |

1-of-8 Data Selector/Multiplexer |

|

| 10 | SN74F153 |

Texas Instruments |

Dual 1-of-4 Data Selectors/Multiplexer |

|

| 11 | SN74F157A |

Texas Instruments |

Quadruple 2-Line To 1-Line Data Selectors/Multiplexer |

|

| 12 | SN74F158A |

Texas Instruments |

Quadruple 2-Line To 1-Line Data Selectors/Multiplexers |

|