The 128Mb DDR SDRAM is a high-speed CMOS, dynamic random-access memory containing 134,217,728 bits. It is internally configured as a quad-bank DRAM. Read or Write command are used to select the bank and the starting column location for the burst access. The DDR SDRAM provides for programmable Read or Write The 128Mb DDR SDRAM uses a double-data-rate archite.

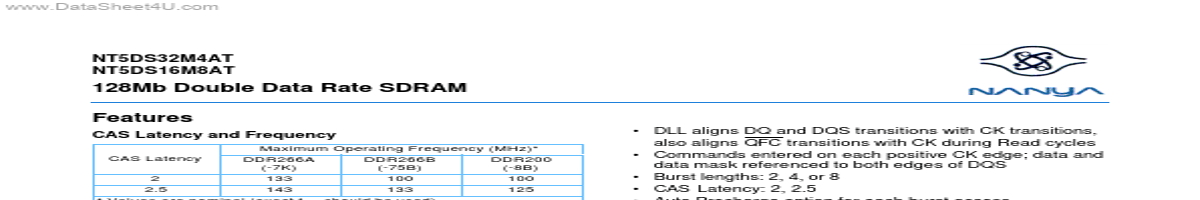

CAS Latency and Frequency

Maximum Operating Frequency (MHz)

* DDR266A DDR266B DDR200 (-7K) (-75B) (-8B) 2 133 100 100 2.5 143 133 125

* Values are nominal (exact tCK should be used). CAS Latency

• Double data rate architecture: two data transfers per clock cycle

• Bidirectional data strobe (DQS) is transmitted and received with data, to be used in capturing data at the receiver

• DQS is edge-aligned with data for reads and is centeraligned with data for writes

• Differential clock inputs (CK and CK)

• Four internal banks for concurrent operation

• Data mask (DM) for write data

• DLL aligns DQ.

| No. | Partie # | Fabricant | Description | Fiche Technique |

|---|---|---|---|---|

| 1 | NT5DS32M4AW |

Nanya Technology |

(NT5DSxxMxAx) 128Mb DDR333/300 SDRAM |

|

| 2 | NT5DS32M16AF |

Nanya Techology |

(NT5DSxxMxAF) 512Mb DDR SDRAM |

|

| 3 | NT5DS32M16BF |

Nanya Techology |

(NT5DSxxMxBx) 512Mb DDR SDRAM |

|

| 4 | NT5DS32M16BG |

Nanya Techology |

(NT5DSxxMxBx) 512Mb DDR SDRAM |

|

| 5 | NT5DS32M16BS |

Nanya Techology |

(NT5DSxxMxBx) 512Mb DDR SDRAM |

|

| 6 | NT5DS32M16BT |

Nanya Techology |

(NT5DSxxMxBx) 512Mb DDR SDRAM |

|

| 7 | NT5DS32M16CG |

Nanya Techology |

512Mb DDR SDRAM |

|

| 8 | NT5DS32M16CS |

Nanya Techology |

512Mb DDR SDRAM |

|

| 9 | NT5DS32M16DS |

Nanya Techology |

512Mb DDR SDRAM |

|

| 10 | NT5DS32M8AT |

Nanya |

256Mb DDR333/300 SDRAM |

|

| 11 | NT5DS32M8AW |

Nanya |

(NT5DSxxMxAx) 256Mb DDR333/300 SDRAM |

|

| 12 | NT5DS32M8BF |

Nanya Techology |

(NT5DSxxMxBx) 256Mb DDR SDRAM |

|