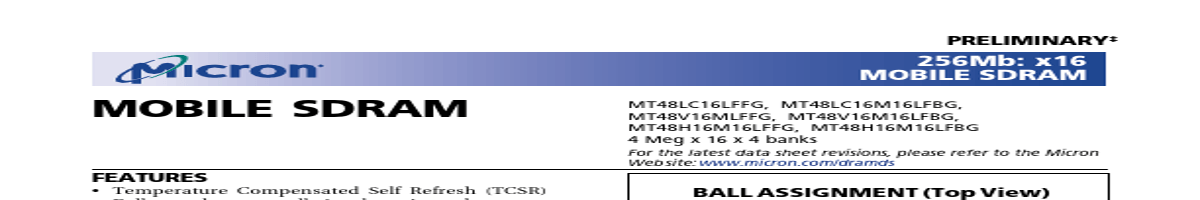

The 256Mb SDRAM is a high-speed CMOS, dynamic random-access memory containing 268,435,456 bits. It is internally configured as a quadbank DRAM with a synchronous interface (all signals are registered on the positive edge of the clock signal, CLK). Each of the x16’s 67,108,864-bit banks is organized as 8,192 rows by 512 columns by 16 bits. Read and write acce.

• Temperature Compensated Self Refresh (TCSR)

• Fully synchronous; all signals registered on positive edge of system clock

• Internal pipelined operation; column address can be changed every clock cycle

• Internal banks for hiding row access/precharge

• Programmable burst lengths: 1, 2, 4, 8, or full page

• Auto Precharge, includes CONCURRENT AUTO PRECHARGE and Auto Refresh Modes

• Self Refresh Mode

• 64ms, 8,192-cycle refresh

• LVTTL-compatible inputs and outputs

• Low voltage power supply

• Deep Power Down

• Partial Array Self Refresh power-saving mode

MT48LC16LFFG, MT48LC16M16LFBG, MT48V16.

| No. | Partie # | Fabricant | Description | Fiche Technique |

|---|---|---|---|---|

| 1 | MT48H16M16LF |

Micron Technology |

(MT48H16M16LF / MT48H16M32LF) 16 Meg x 32 Mobile SDRAM |

|

| 2 | MT48H16M16LFBG |

Micron Technology |

256M x 16 Mobile SDRAM |

|

| 3 | MT48H16M32LF |

Micron Technology |

Mobile LPSDR SDRAM |

|

| 4 | MT48H16M32LG |

Micron Technology |

(MT48H16M16LF / MT48H16M32LF) 16 Meg x 32 Mobile SDRAM |

|

| 5 | MT48H16M32LG |

Micron Technology |

Mobile LPSDR SDRAM |

|

| 6 | MT48H32M16LF |

Micron Technology |

Mobile LPSDR SDRAM |

|

| 7 | MT48H32M32LF |

Micron Technology |

Mobile LPSDR SDRAM |

|

| 8 | MT48H32M32LG |

Micron Technology |

Mobile LPSDR SDRAM |

|

| 9 | MT48H4M16LF |

Micron Technology |

Mobile SDRAM |

|

| 10 | MT48H4M32LF |

Micron Technology |

Mobile Low-Power SDR SDRAM |

|

| 11 | MT48H8M16LF |

Micron Technology |

Synchronous DRAM |

|

| 12 | MT48H8M32LF |

Micron Technology |

Mobile Low-Power SDR SDRAM |

|