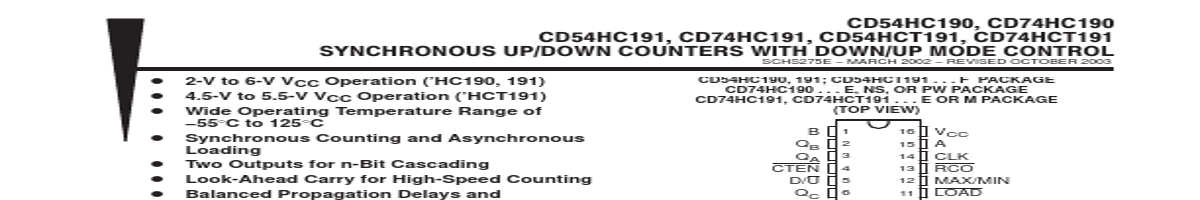

ordering information The CD54/74HC190 are asynchronously presettable BCD decade counters, whereas the CD54/74HC191 and CD54/74HCT191 are asynchronously presettable binary counters. Presetting the counter to the number on preset data inputs (A−D) is accomplished by a low asynchronous parallel load (LOAD) input. Counting occurs when LOAD is high, count enable .

y counters. Presetting the counter to the number on preset data inputs (A−D) is accomplished by a low asynchronous parallel load (LOAD) input. Counting occurs when LOAD is high, count enable (CTEN) is low, and the down/up (D/U) input is either high for down counting or low for up counting. The counter is decremented or incremented synchronously with the low-to-high transition of the clock. ORDERING INFORMATION TA PACKAGE† ORDERABLE PART NUMBER TOP-SIDE MARKING CD74HC190E CD74HC190E PDIP − E Tube of 25 CD74HC191E CD74HCT191E CD74HC191E CD74HCT191E Tube of 40 CD74HC191M SOIC − M R.

| No. | Partie # | Fabricant | Description | Fiche Technique |

|---|---|---|---|---|

| 1 | CD54HC190 |

Texas Instruments |

Synchronous Up/Down Counters |

|

| 2 | CD54HC192 |

Texas Instruments |

Presettable Synchronous 4-Bit Up/Down Counters |

|

| 3 | CD54HC193 |

Texas Instruments |

Presettable Synchronous 4-Bit Up/Down Counters |

|

| 4 | CD54HC194 |

Texas Instruments |

4-Bit Bidirectional Universal Shift Register |

|

| 5 | CD54HC195 |

Texas Instruments |

4-Bit Parallel Access Register |

|

| 6 | CD54HC10 |

Texas Instruments |

Triple 3-Input NAND Gates |

|

| 7 | CD54HC107 |

Texas Instruments |

Dual J-K Flip-Flop |

|

| 8 | CD54HC109 |

Texas Instruments |

Dual J-K Flip-Flop |

|

| 9 | CD54HC10F |

Texas Instruments |

Triple 3-Input NAND Gates |

|

| 10 | CD54HC11 |

Texas Instruments |

Triple 3-Input AND Gate |

|

| 11 | CD54HC112 |

Texas Instruments |

Dual J-K Flip-Flop |

|

| 12 | CD54HC11F |

Texas Instruments |

Triple 3-Input AND Gate |

|