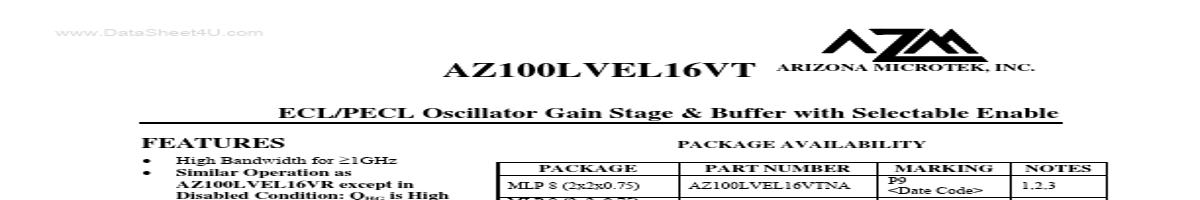

Add R1 at end of part number for 7 inch (1K parts), R2 for 13 inch (2.5K parts) Tape & Reel. Date code format: “Y” or “YY” for year followed by “WW” for week. Parts marked TNA for date codes prior to 4WW (prior to 2004). Parts marked TNB for date codes prior to 4WW (prior to 2004). Parts marked TNC for date codes prior to 4WW (prior to 2004). Waffle Pack T.

•

•

•

•

•

•

• High Bandwidth for ≥1GHz Similar Operation as AZ100LVEL16VR except in Disabled Condition: QHG is High Operating Range of 3.0V to 5.5V Minimizes External Components Selectable Enable Polarity and Threshold (CMOS/TTL or PECL) Available in a 3x3 mm or 2x2 mm MLP Package S-Parameter (.s2p) and IBIS Model Files Available on Arizona Microtek Website PACKAGE

MLP 8 (2x2x0.75) MLP 8 (2x2x0.75) RoHS Compliant / Lead (Pb) Free MLP 8 (2x2x0.75) MLP 8 (2x2x0.75) RoHS Compliant / Lead (Pb) Free MLP 8 (2x2x0.75) MLP 8 (2x2x0.75) RoHS Compliant / Lead (Pb) Free MLP 8 (2x2x0.75) MLP 8 (2x2x0.75) .

| No. | Partie # | Fabricant | Description | Fiche Technique |

|---|---|---|---|---|

| 1 | AZ100LVEL16VR |

ETC |

ECL/PECL Oscillator Gain Stage & Buffer with Selectable Enable |

|

| 2 | AZ100LVEL16VRL |

ETC |

ECL/PECL Oscillator Gain Stage & Buffer with Selectable Enable |

|

| 3 | AZ100LVEL16VRLR1 |

ETC |

ECL/PECL Oscillator Gain Stage & Buffer with Selectable Enable |

|

| 4 | AZ100LVEL16VRLR2 |

ETC |

ECL/PECL Oscillator Gain Stage & Buffer with Selectable Enable |

|

| 5 | AZ100LVEL16VRX |

ETC |

ECL/PECL Oscillator Gain Stage & Buffer with Selectable Enable |

|

| 6 | AZ100LVEL16VS |

Arizona Microtek |

ECL/PECL Differential Receiver |

|

| 7 | AZ100LVEL16VV |

Arizona Microtek |

Dual Frequency ECL/PECL Oscillator Gain Stage & Buffer |

|

| 8 | AZ100LVEL16 |

Arizona Microtek |

ECL/PECL Differential Receiver |

|

| 9 | AZ100LVEL11 |

Arizona Microtek |

ECL/PECL 1:2 Differential Fanout Buffer |

|

| 10 | AZ100LVEL32 |

Arizona Microtek |

ECL/PECL / 2 Divider |

|

| 11 | AZ100LVEL33 |

Arizona Microtek |

ECL/PECL / 4 Divider |

|

| 12 | AZ100LVEL58 |

Arizona Microtek |

ECL/PECL 2:1 Multiplexer |

|