www.ti.com PACKAGE OPTION ADDENDUM 4-Dec-2021 PACKAGING INFORMATION Orderable Device Status Package Type Package Pins Package Eco Plan (1) Drawing Qty (2) JM38510/30109BEA JM38510/30109BFA JM38510/30109BFA M38510/30109BEA M38510/30109BEA M38510/30109BFA M38510/30109BFA SN54LS109AJ SN54LS109AJ SN74LS109AD SN74LS109AD SN74LS109ADR SN74LS109ADR SN74LS1.

0 RoHS & Green D 16 2500 RoHS & Green N 16 25 RoHS & Green N 16 25 RoHS & Green N 16 25 RoHS & Green Lead finish/ Ball material (6) SNPB SNPB SNPB SNPB SNPB SNPB SNPB SNPB SNPB NIPDAU NIPDAU NIPDAU NIPDAU NIPDAU NIPDAU NIPDAU NIPDAU NIPDAU MSL Peak Temp Op Temp (°C) (3) N / A for Pkg Type -55 to 125 N / A for Pkg Type -55 to 125 N / A for Pkg Type -55 to 125 N / A for Pkg Type -55 to 125 N / A for Pkg Type -55 to 125 N / A for Pkg Type -55 to 125 N / A for Pkg Type -55 to 125 N / A for Pkg Type -55 to 125 N / A for Pkg Type -55 to 125 Level-1-260C-UNLIM Level-1-260C-UNLIM.

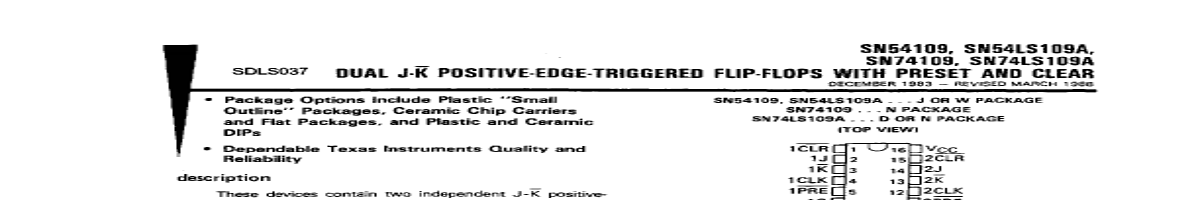

www.DataSheet4U.com SN74LS109A Dual JK Positive Edge-Triggered Flip-Flop The SN74LS109A consists of two high speed comp.

| No. | Partie # | Fabricant | Description | Fiche Technique |

|---|---|---|---|---|

| 1 | 74LS109 |

Agere Systems |

Dual J-K Flip-Flop |

|

| 2 | 74LS10 |

ON Semiconductor |

TRIPLE 3-INPUT NAND GATE |

|

| 3 | 74LS10 |

Fairchild Semiconductor |

Triple 3-Input NAND Gate |

|

| 4 | 74LS107 |

ETC |

Dual Negative-Edge-Triggered Master-Slave J-K Flip-Flops |

|

| 5 | 74LS11 |

Fairchild Semiconductor |

Triple 3-Input AND Gate |

|

| 6 | 74LS112 |

Hitachi Semiconductor |

Dual J-K Negative-edge-triggered Flip-Flops |

|

| 7 | 74LS112A |

Motorola |

DUAL JK NEGATIVE EDGE-TRIGGERED FLIP-FLOP |

|

| 8 | 74LS112A |

Fairchild Semiconductor |

Dual Negative-Edge-Triggered Master-Slave J-K Flip-Flop |

|

| 9 | 74LS114A |

Motorola |

DUAL JK NEGATIVE EDGE-TRIGGERED FLIP-FLOP |

|

| 10 | 74LS12 |

Hitachi Semiconductor |

Dual Retriggerable Monostable Multivibrators |

|

| 11 | 74LS12 |

Fairchild Semiconductor |

Dual Retriggerable One-Shot |

|

| 12 | 74LS12 |

ON Semiconductor |

LOW POWER SCHOTTKY |

|