Recherchez avec le numéro de pièce ainsi que le fabricant ou la description

S3P72F5 |

| Part Number | S3P72F5 |

| Manufacturer | Samsung semiconductor |

| Description | Table 1–1. S3C72F5 Pin Descriptions Pin Name P0.0 P0.1 P0.2 P0.3 Pin Type I/O Description 4-bit I/O port. 1-bit and 4-bit read/write and test are possible. Individual pins are software configurable a... |

| Features |

SUMMARY

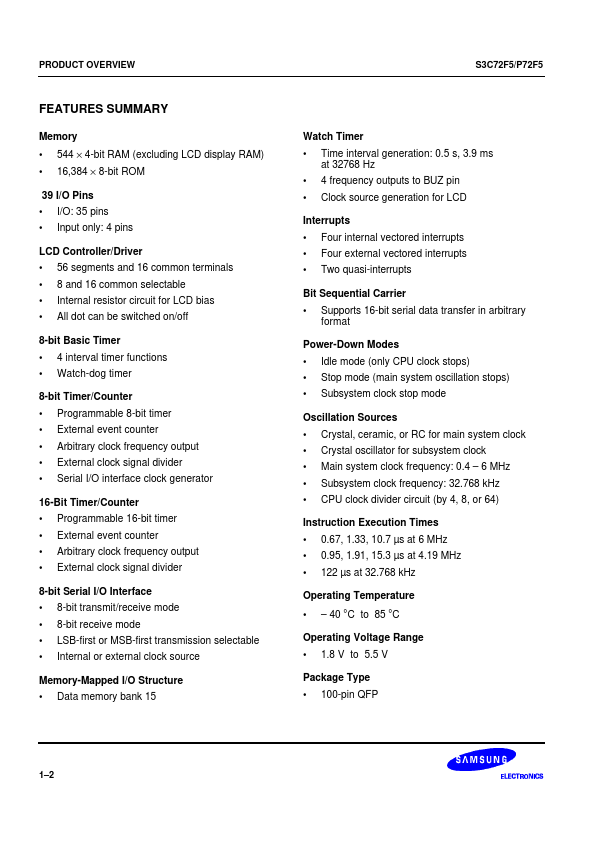

Memory • • 544 × 4-bit RAM (excluding LCD display RAM) 16,384 × 8-bit ROM Watch Timer • • • Time interval generation: 0.5 s, 3.9 ms at 32768 Hz 4 frequency outputs to BUZ pin Clock source generation for LCD 39 I/O Pins • • I/O: 35 pins Input only: 4 pins Interrupts • Four internal vectored interrupts Four external vectored interrupts Two quasi-interrupts • • LCD Controller/Driver • • • • 56 segments and 16 common terminals 8 and 16 common selectable Internal resistor circuit for LCD bias All dot can be switched on/off Bit Sequential Carrier • Supports 16-bit serial data transfer in... |

| Document |

PDF 263.99KB |

| Distributor | Stock | Price | Buy |

|---|

| No. | Parte # | Fabricante | Descripción | Hoja de Datos |

|---|---|---|---|---|

| 1 | S3P7235 |

Samsung semiconductor |

The S3C7238/C7235 single-chip CMOS microcontroller has been designed for high performance using Samsungs newest 4-bit CPU core/ SAM47 (Samsung Arrange |

|

| 2 | S3P7238 |

Samsung semiconductor |

The S3C7238/C7235 single-chip CMOS microcontroller has been designed for high performance using Samsungs newest 4-bit CPU core/ SAM47 (Samsung Arrange |

|

| 3 | S3P7295 |

Samsung semiconductor |

The S3C7295 single-chip CMOS microcontroller has been designed for high performance using Samsungs newest 4-bit CPU core/ SAM47 (Samsung Arrangeable M |

|

| 4 | S3P72B9 |

Samsung semiconductor |

The S3C72B5/C72B7/C72B9 single-chip CMOS microcontroller has been designed for high performance using Samsungs newest 4-bit CPU core/ SAM47 (Samsung A |

|

| 5 | S3P72C8 |

Samsung semiconductor |

The S3C72C8 single-chip CMOS microcontroller has been designed for high performance using Samsungs newest 4-bit CPU core/ SAM47 (Samsung Arrangeable M |

|