Recherchez avec le numéro de pièce ainsi que le fabricant ou la description

74LS112A |

| Part Number | 74LS112A |

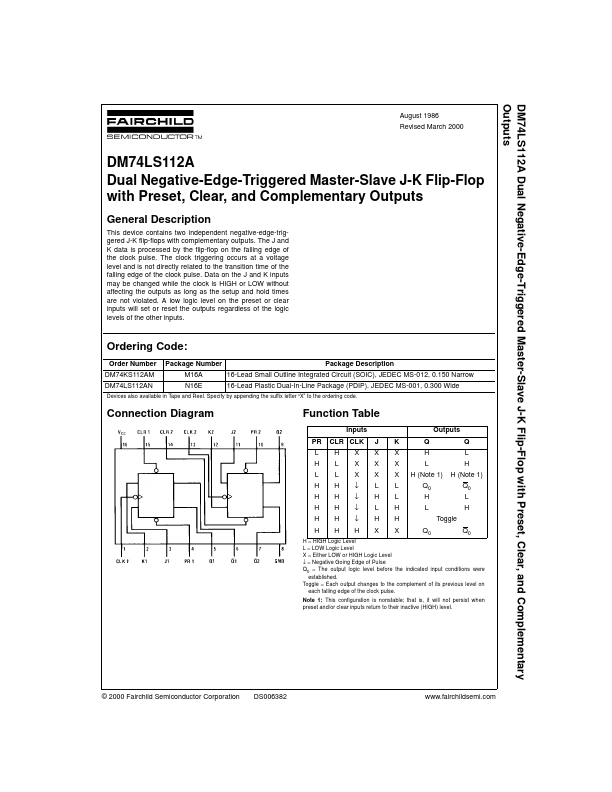

| Manufacturer | Fairchild Semiconductor |

| Description | This device contains two independent negative-edge-triggered J-K flip-flops with complementary outputs. The J and K data is processed by the flip-flop on the falling edge of the clock pulse. The clock... |

| Features |

... |

| Document |

PDF 52.01KB |

| Distributor | Stock | Price | Buy |

|---|

| No. | Parte # | Fabricante | Descripción | Hoja de Datos |

|---|---|---|---|---|

| 1 | 74LS112 |

Hitachi Semiconductor |

Dual J-K Negative-edge-triggered Flip-Flops |

|

| 2 | 74LS112A |

Motorola |

DUAL JK NEGATIVE EDGE-TRIGGERED FLIP-FLOP |

|

| 3 | 74LS11 |

Fairchild Semiconductor |

Triple 3-Input AND Gate |

|

| 4 | 74LS114A |

Motorola |

DUAL JK NEGATIVE EDGE-TRIGGERED FLIP-FLOP |

|

| 5 | 74LS10 |

ON Semiconductor |

TRIPLE 3-INPUT NAND GATE |

|