...... 4 1.1 DDR Center Aligned Read Strobe Functionality (DCARS) .... 6 1.2 Error Detection and Correction Functionality. 6 2. Connection Diagram...... 9 2.1 FBGA 24-Ball 5 x 5 Array Footprint ..

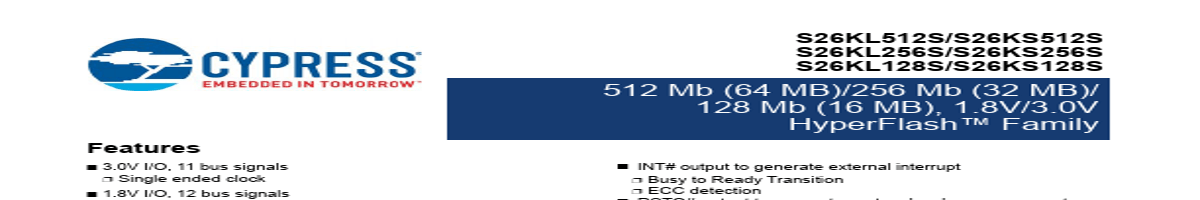

■ 3.0V I/O, 11 bus signals

❐ Single ended clock

■ 1.8V I/O, 12 bus signals

❐ Differential clock (CK, CK#)

■ Chip Select (CS#)

■ 8-bit data bus (DQ[7:0])

■ Read-Write Data Strobe (RWDS)

❐ HyperFlash™ memories use RWDS only as a Read Data Strobe

■ Up to 333 MBps sustained read throughput

■ DDR

– two data transfers per clock

■ 166-MHz clock rate (333 MBps) at 1.8V VCC

■ 100-MHz clock rate (200 MBps) at 3.0V VCC

■ 96-ns initial random read access time

❐ Initial random access read latency: 5 to 16 clock cycles

■ Sequential burst transactions

■ Configurable Burst Characteristics

❐ Wrapped burst leng.

| No. | Partie # | Fabricant | Description | Fiche Technique |

|---|---|---|---|---|

| 1 | S26KS256S |

Cypress Semiconductor |

high-speed CMOS MirrorBit NOR flash devices |

|

| 2 | S26KS256S |

Infineon |

256Mb (32MB) HYPER FLASH |

|

| 3 | S26KS512S |

Cypress Semiconductor |

high-speed CMOS MirrorBit NOR flash devices |

|

| 4 | S26KS512S |

Infineon |

512Mb (64MB) HYPER FLASH |

|

| 5 | S26KL128S |

Cypress Semiconductor |

high-speed CMOS MirrorBit NOR flash devices |

|

| 6 | S26KL128S |

Infineon |

128Mb (16MB) HYPER FLASH |

|

| 7 | S26KL256S |

Cypress Semiconductor |

high-speed CMOS MirrorBit NOR flash devices |

|

| 8 | S26KL256S |

Infineon |

256Mb (32MB) HYPER FLASH |

|

| 9 | S26KL512S |

Cypress Semiconductor |

high-speed CMOS MirrorBit NOR flash devices |

|

| 10 | S26KL512S |

Infineon |

512Mb (64MB) HYPER FLASH |

|

| 11 | S26 |

Fairchild Semiconductor |

Schottky Rectifiers |

|

| 12 | S2600B |

ETC |

HIGH VOLTAGE MEDIUM CURRENT SILICON CONTROLLED RECTIFIERS |

|