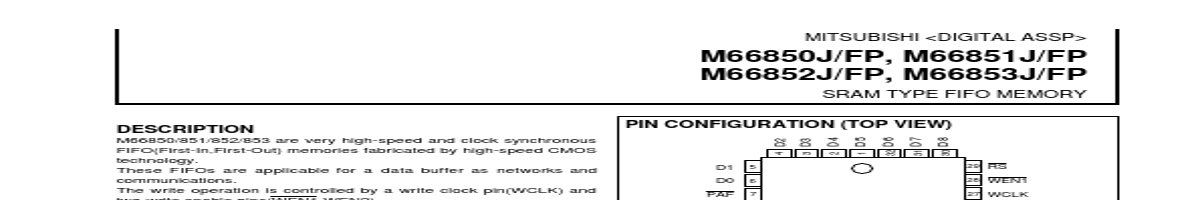

M66850/851/852/853 are very high-speed and clock synchronous FIFO(First-In,First-Out) memories fabricated by high-speed CMOS technology. These FIFOs are applicable for a data buffer as networks and communications. The write operation is controlled by a write clock pin(WCLK) and two write enable pins(WEN1,WEN2). Data present at the data input pins(D0-D8) is w.

• Memory configuration 64words x 9bits (M66850J/FP) 256words x 9bits (M66851J/FP) 512words x 9bits (M66852J/FP) 1024words x 9bits (M66853J/FP) Write and Read Clocks can be independent Advanced CMOS technology Programmable Almost-Empty and Almost-Full flags High-speed : 25ns cycle time Package Available : 32-pin Pastic Leaded Chip Carrier(PLCC) 32-pin Low profile Quad Flat Package(LQFP)

D1 D0 PAF PAE GND

1 2 3 4 5

•

•

•

•

•

REN1 6 RCLK 7 REN2 8 EF 10 FF 11 Q2 14 Q3 15 Q0 12 OE 9 Q1 13 Q4 16 LD

APPLICATION

• Data Buffer for networks communications.

Outline 32P6B(M66850

– 853FP)

BLOCK DIAGRA.

| No. | Partie # | Fabricant | Description | Fiche Technique |

|---|---|---|---|---|

| 1 | M66852J |

Mitsubishi |

SRAM TYPE FIFO MEMORY |

|

| 2 | M66850FP |

Mitsubishi |

SRAM TYPE FIFO MEMORY |

|

| 3 | M66850J |

Mitsubishi |

SRAM TYPE FIFO MEMORY |

|

| 4 | M66851FP |

Mitsubishi |

SRAM TYPE FIFO MEMORY |

|

| 5 | M66851J |

Mitsubishi |

SRAM TYPE FIFO MEMORY |

|

| 6 | M66853FP |

Mitsubishi |

SRAM TYPE FIFO MEMORY |

|

| 7 | M66853J |

Mitsubishi |

SRAM TYPE FIFO MEMORY |

|

| 8 | M66 |

Micro Electronics |

IMPLE MELODY GENERATOR |

|

| 9 | M660 |

Integrated Circuit Systems |

DUAL SAW / SELECTABLE FREQUENCY VCSO |

|

| 10 | M660-01 |

Integrated Circuit Systems |

Voltage Controlled SAW Oscillator |

|

| 11 | M660-02 |

Integrated Circuit Systems |

DUAL SAW / SELECTABLE FREQUENCY VCSO |

|

| 12 | M66004FP |

Mitsubishi |

null16-DIGIT 5x7-SEGMENT VFD CONTROLLER |

|