The Intersil HCS573MS is a Radiation Hardened octal transparent three-state latch with an active low output enable. The HCS573MS utilizes advanced CMOS/SOS technology. The outputs are transparent to the inputs when the Latch Enable (LE) is HIGH. When the Latch Enable (LE) goes LOW, the data is latched. The Output Enable (OE) controls the tri-state outputs. W.

•

•

•

•

•

•

•

•

•

•

•

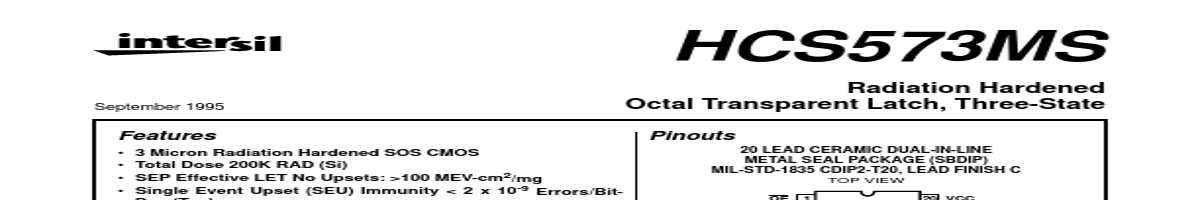

• 3 Micron Radiation Hardened SOS CMOS Total Dose 200K RAD (Si) SEP Effective LET No Upsets: >100 MEV-cm2/mg Single Event Upset (SEU) Immunity < 2 x 10-9 Errors/BitDay (Typ) Dose Rate Survivability: >1 x 1012 RAD (Si)/s Dose Rate Upset >1010 RAD (Si)/s 20ns Pulse Latch-Up Free Under Any Conditions Fanout (Over Temperature Range) - Bus Driver Outputs - 15 LSTTL Loads Military Temperature Range: -55oC to +125oC Significant Power Reduction Compared to LSTTL ICs DC Operating Voltage Range: 4.5V to 5.5V Input Logic Levels - VIL = 0.3 VCC Max - VIH = 0.7 VCC Min Input Current Le.

| No. | Partie # | Fabricant | Description | Fiche Technique |

|---|---|---|---|---|

| 1 | HCS500 |

Microchip Technology |

KEELOQ CODE HOPPING ENCODER |

|

| 2 | HCS50R150V |

SemiHow |

500V N-Channel Super Junction MOSFET |

|

| 3 | HCS512 |

Microchip Technology |

KEELOQ CODE HOPPING DECODER |

|

| 4 | HCS515 |

Microchip Technology |

KEELOQ CODE HOPPING DECODER |

|

| 5 | HCS55R140E |

SemiHow |

N-Channel MOSFET |

|

| 6 | HCS5931 |

HITANO |

METAL STRIP CURRENT SENSING RESISTORS |

|

| 7 | HCS00MS |

Intersil Corporation |

Radiation Hardened Quad 2-Input NAND Gate |

|

| 8 | HCS02MS |

Intersil Corporation |

Radiation Hardened Quad 2-Input NOR Gate |

|

| 9 | HCS04MS |

Intersil Corporation |

Radiation Hardened Hex Inverter |

|

| 10 | HCS05MS |

Intersil Corporation |

Radiation Hardened Hex Inverter with Open Drain |

|

| 11 | HCS08 |

Freescale Semiconductor |

Microcontrollers |

|

| 12 | HCS0805 |

HITANO |

METAL STRIP CURRENT SENSING RESISTORS |

|