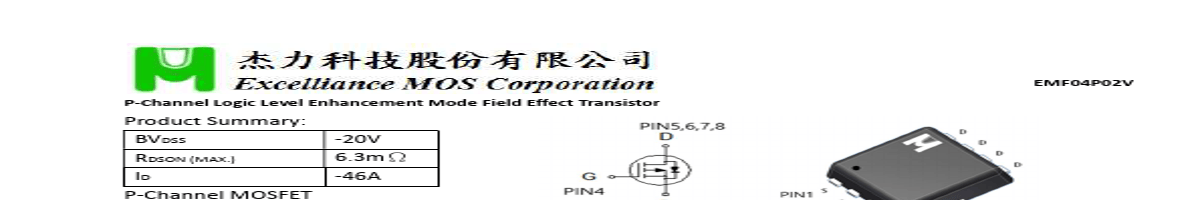

P-Channel Logic Level Enhancement Mode Field Effect Transistor Product Summary: BVDSS -20V RDSON (MAX.) 6.3mΩ ID -46A P-Channel MOSFET UIS, Rg 100% Tested Pb-Free Lead Plating & Halogen Free ABSOLUTE MAXIMUM RATINGS (TA = 25 °C Unless Otherwise Noted) PARAMETERS/TEST CONDITIONS SYMBOL LIMITS Gate-Source Voltage VGS ±12 Continuous Drain Curr.

h limited by maximum junction temperature. 2Duty cycle 1% 2019/6/25 EMF04P02V UNIT V A mJ W W °C UNIT °C / W p.1 350°C / W when mounted on a 1 in2 pad of 2 oz copper. ELECTRICAL CHARACTERISTICS (TJ = 25 °C, Unless Otherwise Noted) PARAMETER SYMBOL TEST CONDITIONS EMF04P02V LIMITS UNIT MIN TYP MAX STATIC Drain-Source Breakdown Voltage Gate Threshold Voltage Gate-Body Leakage Zero Gate Voltage Drain Current On-State Drain Current1 Drain-Source On-State Resistance1 Forward Transconductance1 V(BR)DSS VGS(th) IGSS IDSS ID(ON) RDS(ON) gfs VGS = 0V, ID = -250A VDS = VGS, ID = -250A.

| No. | Partie # | Fabricant | Description | Fiche Technique |

|---|---|---|---|---|

| 1 | EMF04P02H |

Excelliance MOS |

P-Channel Logic Level Enhancement Mode Field Effect Transistor |

|

| 2 | EMF02P02H |

Excelliance MOS |

P-Channel Logic Level Enhancement Mode Field Effect Transistor |

|

| 3 | EMF09P02A |

Excelliance MOS |

P-Channel Logic Level Enhancement Mode Field Effect Transistor |

|

| 4 | EMF09P02CS |

Excelliance MOS |

P-Channel Logic Level Enhancement Mode Field Effect Transistor |

|

| 5 | EMF09P02V |

Excelliance MOS |

P-Channel Logic Level Enhancement Mode Field Effect Transistor |

|

| 6 | EMF11N02J |

Excelliance MOS |

MOSFET |

|

| 7 | EMF14A02G |

Excelliance MOS |

MOSFET |

|

| 8 | EMF14A02V |

Excelliance MOS |

MOSFET |

|

| 9 | EMF14N02A |

Excelliance MOS |

N-Channel Logic Level Enhancement Mode Field Effect Transistor |

|

| 10 | EMF14N02VAT |

Excelliance MOS |

N-Channel Logic Level Enhancement Mode Field Effect Transistor |

|

| 11 | EMF16P01VAT |

Excelliance MOS |

MOSFET |

|

| 12 | EMF17 |

Rohm |

Power management |

|