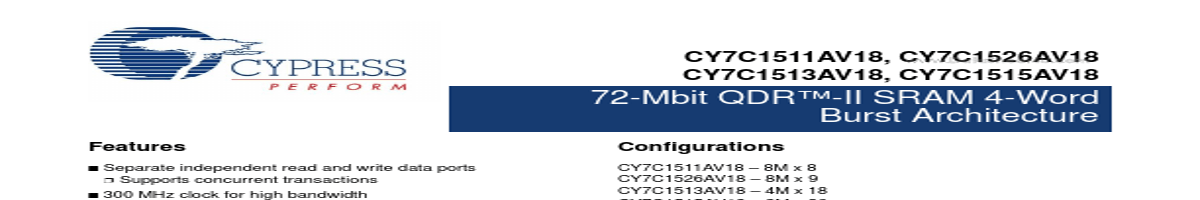

The CY7C1511AV18, CY7C1526AV18, CY7C1513AV18, and CY7C1515AV18 are 1.8V Synchronous Pipelined SRAMs, equipped with QDR™-II architecture. QDR-II architecture consists of two separate ports: the read port and the write port to access the memory array. The read port has dedicated data outputs to support read operations and the write port has dedicated data inpu.

■

Configurations

CY7C1511AV18

– 8M x 8 CY7C1526AV18

– 8M x 9 CY7C1513AV18

– 4M x 18 CY7C1515AV18

– 2M x 36

Separate independent read and write data ports

❐ Supports concurrent transactions 300 MHz clock for high bandwidth 4-word burst for reducing address bus frequency Double Data Rate (DDR) interfaces on both read and write ports (data transferred at 600 MHz) at 300 MHz Two input clocks (K and K) for precise DDR timing

❐ SRAM uses rising edges only Two input clocks for output data (C and C) to minimize clock skew and flight time mismatches Echo clocks (CQ and CQ) simplify data capture in hi.

| No. | Partie # | Fabricant | Description | Fiche Technique |

|---|---|---|---|---|

| 1 | CY7C1511JV18 |

Cypress Semiconductor |

72-Mbit QDR-II SRAM 4-Word Burst Architecture |

|

| 2 | CY7C1511KV18 |

Cypress Semiconductor |

(CY7C15xxKV18) 72-Mbit QDR II SRAM 4-Word Burst Architecture |

|

| 3 | CY7C1511V18 |

Cypress Semiconductor |

(CY7C15xxV18) SRAM 4-Word Burst Architecture |

|

| 4 | CY7C1510AV18 |

Cypress Semiconductor |

72-Mbit QDR-II SRAM 2-Word Burst Architecture |

|

| 5 | CY7C1510V18 |

Cypress Semiconductor |

1.8V Synchronous Pipelined SRAM |

|

| 6 | CY7C1512 |

Cypress Semiconductor |

64K x 8 Static RAM |

|

| 7 | CY7C1512AV18 |

Cypress Semiconductor |

72-Mbit QDR-II SRAM 2-Word Burst Architecture |

|

| 8 | CY7C1512KV18 |

Cypress Semiconductor |

72-Mbit QDR II SRAM Two-Word Burst Architecture |

|

| 9 | CY7C1512V18 |

Cypress Semiconductor |

1.8V Synchronous Pipelined SRAM |

|

| 10 | CY7C1513AV18 |

Cypress Semiconductor |

72-Mbit QDR-II SRAM 4-Word Burst Architecture |

|

| 11 | CY7C1513JV18 |

Cypress Semiconductor |

72-Mbit QDR-II SRAM 4-Word Burst Architecture |

|

| 12 | CY7C1513KV18 |

Cypress Semiconductor |

(CY7C15xxKV18) 72-Mbit QDR II SRAM 4-Word Burst Architecture |

|