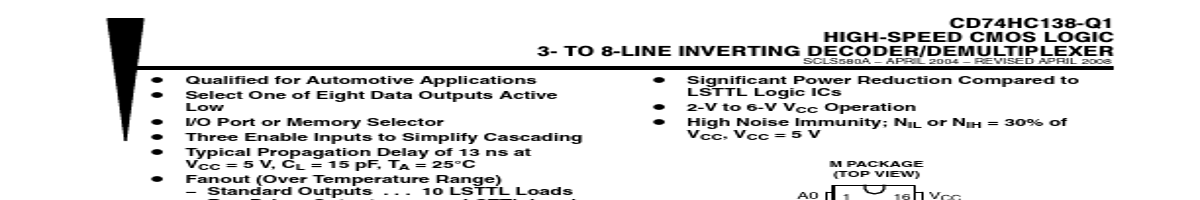

ordering information Y7 7 GND 8 10 Y5 9 Y6 The CD74HC138 is a high-speed silicon-gate CMOS decoder well suited to memory address decoding or data routing applications. This circuit features low power consumption usually associated with CMOS circuitry, yet has speeds comparable to low-power Schottky TTL logic. The circuit has three binary select inputs.

low power consumption usually associated with CMOS circuitry, yet has speeds comparable to low-power Schottky TTL logic. The circuit has three binary select inputs (A0, A1, and A2). If the device is enabled, these inputs determine which one of the eight normally high outputs of the HC138 will go low. Two active-low and one active-high enables (E1, E2, and E3) are provided to ease the cascading of decoders. The decoder’s eight outputs can drive ten low-power Schottky TTL equivalent loads. ORDERING INFORMATION{ TA PACKAGE‡ ORDERABLE PART NUMBER TOP-SIDE MARKING −40°C to 125°C SOIC − M .

| No. | Partie # | Fabricant | Description | Fiche Technique |

|---|---|---|---|---|

| 1 | CD74HC138 |

Texas Instruments |

High-Speed CMOS Logic 3 to 8-Line Decoder/Demultiplexer Inverting/Noninverting |

|

| 2 | CD74HC138E |

Texas Instruments |

High-Speed CMOS Logic 3 to 8-Line Decoder/Demultiplexer Inverting/Noninverting |

|

| 3 | CD74HC138M |

Texas Instruments |

High-Speed CMOS Logic 3 to 8-Line Decoder/Demultiplexer Inverting/Noninverting |

|

| 4 | CD74HC132 |

Texas Instruments |

High-Speed CMOS Logic Quad 2-Input NAND Schmitt Trigger |

|

| 5 | CD74HC137 |

Texas Instruments |

High-Speed CMOS Logic 3 to 8-Line Decoder/Demultiplexer |

|

| 6 | CD74HC139 |

Texas Instruments |

Dual 2- to 4-Line Decoder/Demultiplexer |

|

| 7 | CD74HC10 |

Texas Instruments |

Triple 3-Input NAND Gates |

|

| 8 | CD74HC107 |

Texas Instruments |

Dual J-K Flip-Flop |

|

| 9 | CD74HC109 |

Texas Instruments |

Dual J-K Flip-Flop |

|

| 10 | CD74HC10E |

Texas Instruments |

Triple 3-Input NAND Gates |

|

| 11 | CD74HC10M |

Texas Instruments |

Triple 3-Input NAND Gates |

|

| 12 | CD74HC11 |

Texas Instruments |

Triple 3-Input AND Gate |

|