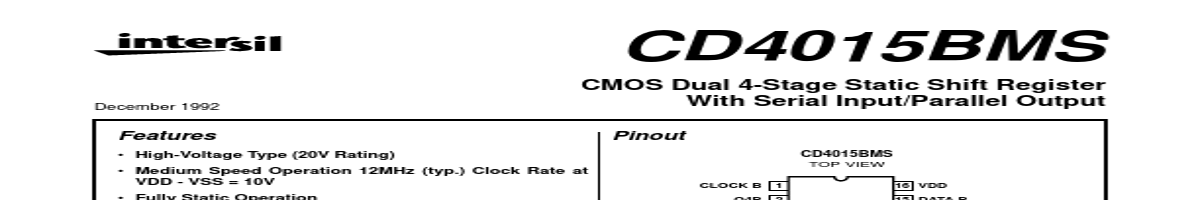

of ‘B’ Series CMOS Devices” Functional Diagram VDD 16 DATA A CLOCK A RESET A 7 9 6 4 STAGE 5 4 3 10 DATA B 15 1 14 RESET B 4 STAGE 13 12 Q2B 11 Q3B 2 Q4B 8 VSS Q1A Q2A Q3A Q4A Q1B Applications • Serial-Input/Parallel-Output Data Queueing • Serial to Parallel Data Conversion • General-Purpose Register Description CD4015BMS consists of two identical, indepe.

• High-Voltage Type (20V Rating)

• Medium Speed Operation 12MHz (typ.) Clock Rate at VDD - VSS = 10V

• Fully Static Operation

• 8 Master-Slave Flip-Flops Plus Input and Output Buffering

• 100% Tested For Quiescent Current at 20V

• 5V, 10V and 15V Parametric Ratings

• Standardized Symmetrical Output Characteristics

• Maximum Input Current of 1µA at 18V Over Full Package-Temperature Range; 100nA at 18V and 25oC

• Noise Margin (Full Package-Temperature Range) = - 1V at VDD = 5V - 2V at VDD = 10V - 2.5V at VDD = 15V

• Meets All Requirements of JEDEC Tentative Standard No. 13B, “Standard Specificati.

| No. | Partie # | Fabricant | Description | Fiche Technique |

|---|---|---|---|---|

| 1 | CD4015BM |

National Semiconductor |

Dual 4-Bit Static Shift Register |

|

| 2 | CD4015BM |

Texas Instruments |

CMOS Dual 4-Stage Static Shift Register |

|

| 3 | CD4015B |

RCA |

CMOS Dual 4-Stage Static Shift Register |

|

| 4 | CD4015B |

Texas Instruments |

CMOS Dual 4-Stage Static Shift Register |

|

| 5 | CD4015BC |

National Semiconductor |

Dual 4-Bit Static Shift Register |

|

| 6 | CD4015BE |

Texas Instruments |

CMOS Dual 4-Stage Static Shift Register |

|

| 7 | CD4015BF |

Texas Instruments |

CMOS Dual 4-Stage Static Shift Register |

|

| 8 | CD4015BF3A |

Texas Instruments |

CMOS Dual 4-Stage Static Shift Register |

|

| 9 | CD4015BT |

Intersil Corporation |

CMOS Dual 4-Stage Static Shift Register |

|

| 10 | CD4015A |

RCA |

CMOS Dual 4-Stage Static Shift Register |

|

| 11 | CD40100B |

RCA |

CMOS 32-Stage Static Left/Right Shift Register |

|

| 12 | CD40100BMS |

Intersil Corporation |

CMOS 32-Stage Static Left/Right Shift Register |

|