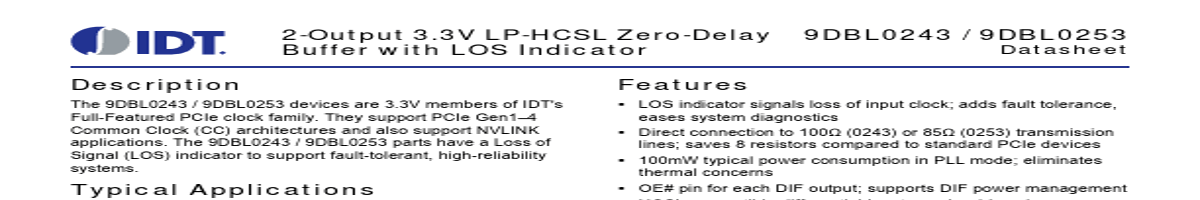

The 9DBL0243 / 9DBL0253 devices are 3.3V members of IDT's Full-Featured PCIe clock family. They support PCIe Gen1–4 Common Clock (CC) architectures and also support NVLINK applications. The 9DBL0243 / 9DBL0253 parts have a Loss of Signal (LOS) indicator to support fault-tolerant, high-reliability systems. Typical Applications ▪ PCIe Gen1–4 and NVLINK clock d.

▪ Loss Of Signal (LOS) open drain output ▪ 2 1

–200 MHz Low-Power (LP) HCSL DIF pairs

— 9DBL0243 default Zout = 100Ω — 9DBL0253 default Zout = 85Ω ▪ Easy AC-coupling to other logic families; see IDT application note AN-891.

Key Specifications

▪ PCIe Gen1

–4 CC compliant in ZDB or fanout buffer mode ▪ Supports NVLINK at 156.25MHz in ZDB or fanout buffer mode ▪ DIF cycle-to-cycle jitter < 5.

| No. | Partie # | Fabricant | Description | Fiche Technique |

|---|---|---|---|---|

| 1 | 9DBL0242 |

Renesas |

Zero-Delay/Fanout Buffer |

|

| 2 | 9DBL0242 |

IDT |

2-output 3.3V PCIe Zero-Delay Buffer |

|

| 3 | 9DBL0242C |

Renesas |

2 to 8-Output 3.3V PCIe Zero-Delay/Fanout Buffers |

|

| 4 | 9DBL02 |

IDT |

2-output 3.3V PCIe Zero-Delay Buffer |

|

| 5 | 9DBL0252 |

Renesas |

Zero-Delay/Fanout Buffer |

|

| 6 | 9DBL0252 |

IDT |

2-output 3.3V PCIe Zero-Delay Buffer |

|

| 7 | 9DBL0252C |

Renesas |

2 to 8-Output 3.3V PCIe Zero-Delay/Fanout Buffers |

|

| 8 | 9DBL0253 |

IDT |

2-Output 3.3V LP-HCSL Zero-Delay Buffer |

|

| 9 | 9DBL0255 |

Renesas |

2 and 4-Output 3.3V PCIe Gen1-5 Clock Fanout Buffers |

|

| 10 | 9DBL0255 |

IDT |

PCIe Gen1-5 Clock Fanout Buffers |

|

| 11 | 9DBL04 |

IDT |

4-output 3.3V PCIe Zero-delay Buffer |

|

| 12 | 9DBL0442 |

Renesas |

3.3V PCIe Zero Delay Buffer |

|