Recherchez avec le numéro de pièce ainsi que le fabricant ou la description

CY7C1511V18 |

| Part Number | CY7C1511V18 |

| Manufacturer | Cypress Semiconductor |

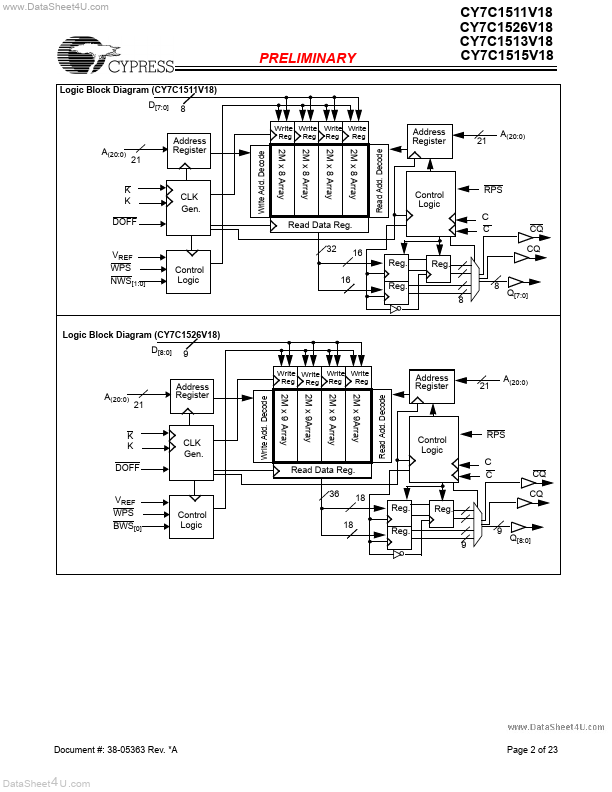

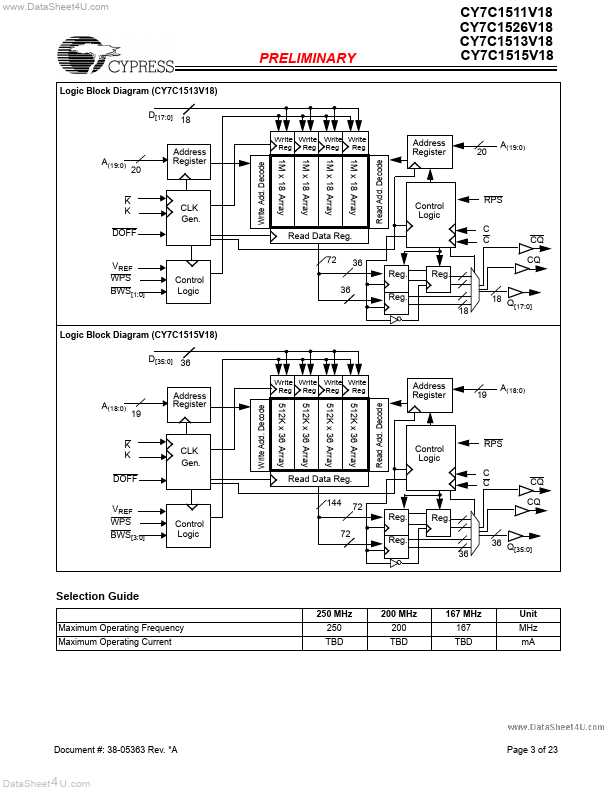

| Description | The CY7C1511V18, CY7C1526V18, CY7C1513V18, and CY7C1515V18 are 1.8V Synchronous Pipelined SRAMs, equipped with QDR-II architecture. QDR-II architecture consists of two separate ports to access the mem... |

| Features |

• Separate Independent Read and Write Data Ports — Supports concurrent transactions • 250-MHz Clock for High Bandwidth • 4-Word Burst for reducing address bus frequency • Double Data Rate (DDR) interfaces on both Read and Write Ports (data transferred at 500 MHz) at 250 MHz • Two input clocks (K and K) for precise DDR timing — SRAM uses rising edges only • Two output clocks (C and C) accounts for clock skew and flight time mismatching • Echo clocks (CQ and CQ) simplify data capture in high speed systems • Single multiplexed address input bus latches address inputs for both Read and Write ports... |

| Document |

PDF 561.73KB |

| Distributor | Stock | Price | Buy |

|---|

| No. | Parte # | Fabricante | Descripción | Hoja de Datos |

|---|---|---|---|---|

| 1 | CY7C1511AV18 |

Cypress Semiconductor |

72-Mbit QDR-II SRAM 4-Word Burst Architecture |

|

| 2 | CY7C1511JV18 |

Cypress Semiconductor |

72-Mbit QDR-II SRAM 4-Word Burst Architecture |

|

| 3 | CY7C1511KV18 |

Cypress Semiconductor |

(CY7C15xxKV18) 72-Mbit QDR II SRAM 4-Word Burst Architecture |

|

| 4 | CY7C1510AV18 |

Cypress Semiconductor |

72-Mbit QDR-II SRAM 2-Word Burst Architecture |

|

| 5 | CY7C1510V18 |

Cypress Semiconductor |

1.8V Synchronous Pipelined SRAM |

|