Recherchez avec le numéro de pièce ainsi que le fabricant ou la description

MC100LVEL39 |

| Part Number | MC100LVEL39 |

| Manufacturer | ON Semiconductor (https://www.onsemi.com/) |

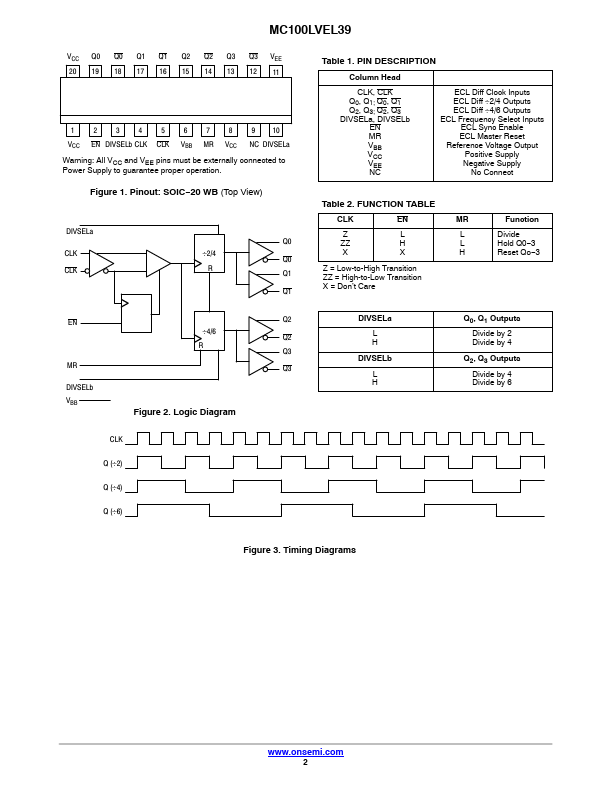

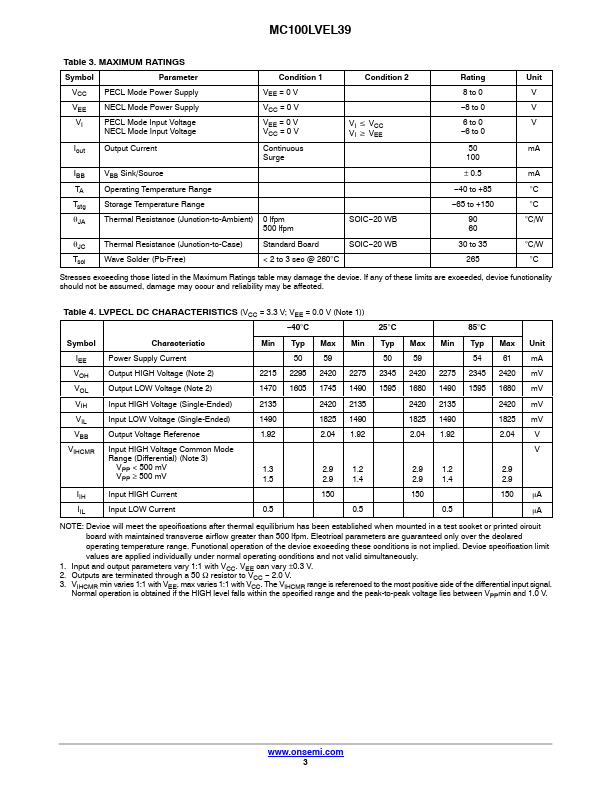

| Description | The MC100LVEL39 is a low skew ÷2/4, ÷4/6 clock generation chip designed explicitly for low skew clock generation applications. The internal dividers are synchronous to each other, therefore, the commo... |

| Features |

www.onsemi.com

SOIC−20 WB DW SUFFIX CASE 751D

MARKING DIAGRAM* 20

100LVEL39 AWLYYWWG

1 A = Assembly Location WL = Wafer Lot YY = Year WW = Work Week G = Pb-Free Package *For additional marking information, refer to Application Note AND8002/D.

• 50 ps Maximum Output-to-Output Skew • Synchronous Enable/Disable • Master Reset for Synchronization ORDERING INFORMATION • ESD Protection: Human Body Model; > 2 kV • The 100 Series Contains Temperature Compensation • PECL Mode Operating Range: VCC = 3.0 V to 3.8 V with VEE = 0 V • NECL Mode Operating Range: VCC = 0 V with VEE = −3.0 V to −3.8 V • ... |

| Document |

PDF 141.03KB |

| Distributor | Stock | Price | Buy |

|---|

| No. | Partie # | Fabricant | Description | Fiche Technique |

|---|---|---|---|---|

| 1 | MC100LVEL30 |

Motorola |

Triple D Flip-Flop |

|

| 2 | MC100LVEL30 |

ON Semiconductor |

Triple D Flip-Flop |

|

| 3 | MC100LVEL31 |

Motorola |

D Flip-Flop |

|

| 4 | MC100LVEL31 |

ON Semiconductor |

3.3V ECL D Flip?Flop |

|

| 5 | MC100LVEL32 |

Motorola |

Divider |

|