Recherchez avec le numéro de pièce ainsi que le fabricant ou la description

74LS75 |

| Part Number | 74LS75 |

| Manufacturer | Fairchild Semiconductor |

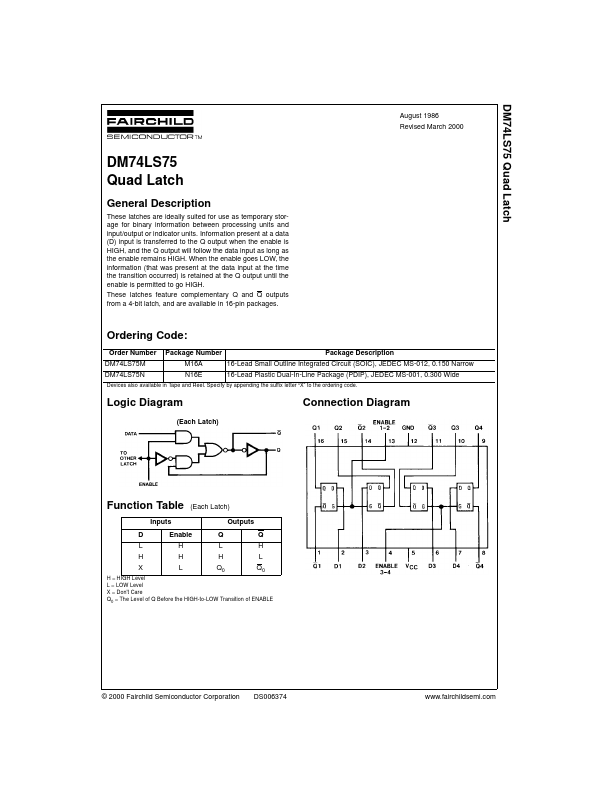

| Description | These latches are ideally suited for use as temporary storage for binary information between processing units and input/output or indicator units. Information present at a data (D) input is transferre... |

| Features |

by appending the suffix letter “X” to the ordering code.

Logic Diagram

(Each Latch)

Connection Diagram

Function Table

Inputs D L H X

(Each Latch) Outputs Q L H Q0 Q H L Q0

Enable H H L

H = HIGH Level L = LOW Level X = Don't Care Q0 = The Level of Q Before the HIGH-to-LOW Transition of ENABLE

© 2000 Fairchild Semiconductor Corporation

DS006374

www.fairchildsemi.com

DM74LS75

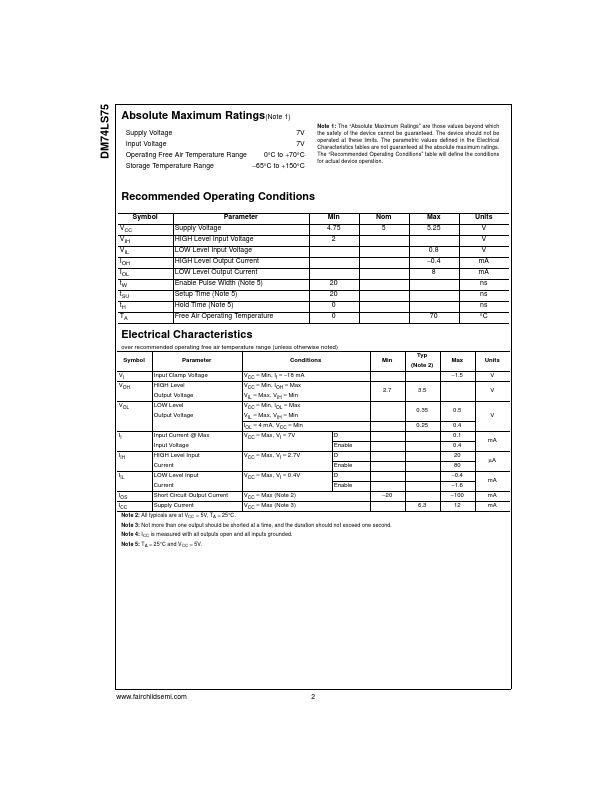

Absolute Maximum Ratings(Note 1)

Supply Voltage Input Voltage Operating Free Air Temperature Range Storage Temperature Range 7V 7V 0°C to +70°C −65°C to +150°C

Note 1: The “Absolute Maximum Ratings” are those val... |

| Document |

PDF 49.81KB |

| Distributor | Stock | Price | Buy |

|---|

| No. | Parte # | Fabricante | Descripción | Hoja de Datos |

|---|---|---|---|---|

| 1 | 74LS73 |

Fairchild Semiconductor |

Dual Negative-Edge-Triggered Master-Slave J-K Flip-Flops |

|

| 2 | 74LS73 |

Hitachi Semiconductor |

Dual J-K Flip-Flops |

|

| 3 | 74LS73 |

Motorola |

DUAL JK NEGATIVE EDGE-TRIGGERED FLIP-FLOP |

|

| 4 | 74LS73A |

Fairchild Semiconductor |

Dual Negative-Edge-Triggered Master-Slave J-K Flip-Flops |

|

| 5 | 74LS73A |

Hitachi Semiconductor |

Dual J-K Flip-Flops |

|