Recherchez avec le numéro de pièce ainsi que le fabricant ou la description

74LS74 |

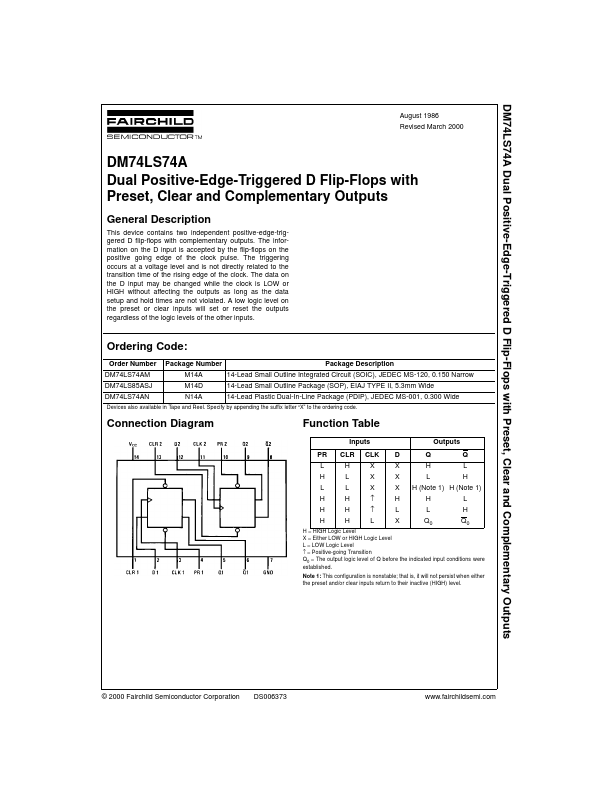

| Part Number | 74LS74 |

| Manufacturer | Fairchild Semiconductor |

| Description | This device contains two independent positive-edge-triggered D flip-flops with complementary outputs. The information on the D input is accepted by the flip-flops on the positive going edge of the clo... |

| Features |

tline Integrated Circuit (SOIC), JEDEC MS-120, 0.150 Narrow 14-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide 14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

Devices also available in Tape and Reel. Specify by appending the suffix letter “X” to the ordering code.

Connection Diagram

Function Table

Inputs PR L H L H H H CLR H L L H H H CLK X X X ↑ ↑ L D X X X H L X Q H L H L Q0 Outputs Q L H L H Q0

H (Note 1) H (Note 1)

H = HIGH Logic Level X = Either LOW or HIGH Logic Level L = LOW Logic Level ↑ = Positive-going Transition Q0 = The output logic level of Q ... |

| Document |

PDF 67.29KB |

| Distributor | Stock | Price | Buy |

|---|

| No. | Parte # | Fabricante | Descripción | Hoja de Datos |

|---|---|---|---|---|

| 1 | 74LS73 |

Fairchild Semiconductor |

Dual Negative-Edge-Triggered Master-Slave J-K Flip-Flops |

|

| 2 | 74LS73 |

Hitachi Semiconductor |

Dual J-K Flip-Flops |

|

| 3 | 74LS73 |

Motorola |

DUAL JK NEGATIVE EDGE-TRIGGERED FLIP-FLOP |

|

| 4 | 74LS73A |

Fairchild Semiconductor |

Dual Negative-Edge-Triggered Master-Slave J-K Flip-Flops |

|

| 5 | 74LS73A |

Hitachi Semiconductor |

Dual J-K Flip-Flops |

|