Recherchez avec le numéro de pièce ainsi que le fabricant ou la description

SN54LS114A |

| Part Number | SN54LS114A |

| Manufacturer | Motorola Inc |

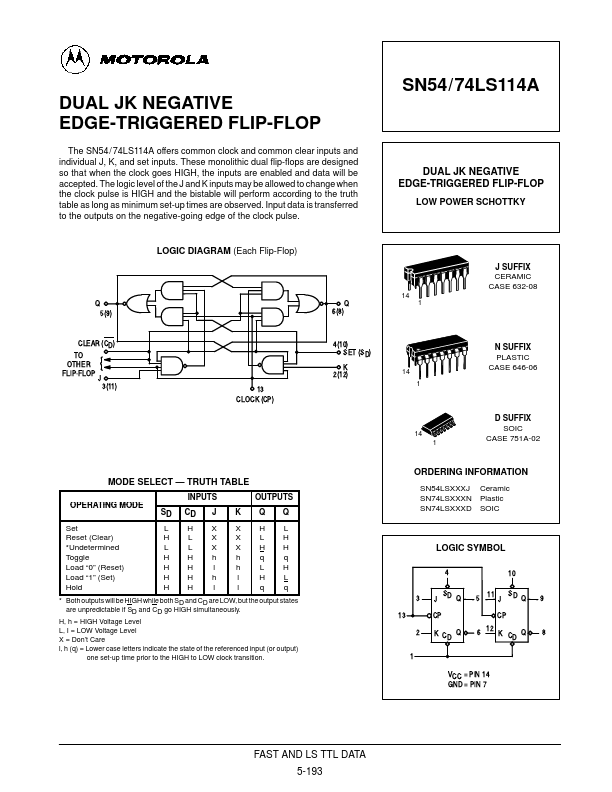

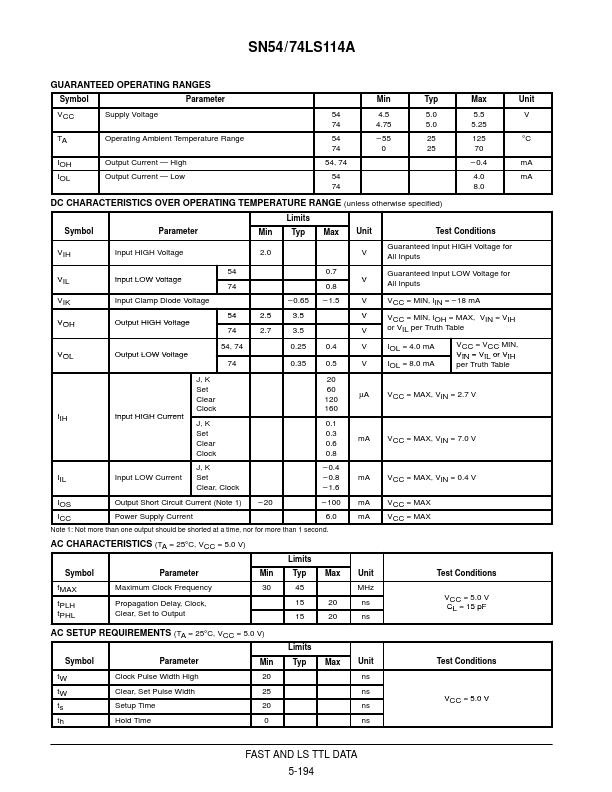

| Description | SN54/74LS114A DUAL JK NEGATIVE EDGE-TRIGGERED FLIP-FLOP The SN54/ 74LS114A offers common clock and common clear inputs and individual J, K, and set inputs. These monolithic dual flip-flops are designe... |

| Features |

Set) Hold L H L H H H H CD H L L H H H H J X X X h l h l K X X X h h l l Q H L H q L H q Q L H H q H L q

3

OUTPUTS

SN54LSXXXJ SN74LSXXXN SN74LSXXXD

Ceramic Plastic SOIC

LOGIC SYMBOL

4 10

* Both outputs will be HIGH while both SD and CD are LOW, but the output states are unpredictable if SD and CD go HIGH simultaneously. H, h = HIGH Voltage Level L, I = LOW Voltage Level X = Don’t Care l, h (q) = Lower case letters indicate the state of the referenced input (or output) l, h (q) = one set-up time prior to the HIGH to LOW clock transition.

J CP

SD

Q

5

11

J CP

SD

Q

9

13

2

K

CD

Q... |

| Document |

PDF 146.38KB |

| Distributor | Stock | Price | Buy |

|---|

| No. | Parte # | Fabricante | Descripción | Hoja de Datos |

|---|---|---|---|---|

| 1 | SN54LS11 |

Motorola Inc |

TRIPLE 3-INPUT AND GATE |

|

| 2 | SN54LS11 |

Texas Instruments |

TRIPLE 3-INPUT POSITIVE-AND GATES |

|

| 3 | SN54LS112A |

Motorola Inc |

DUAL JK NEGATIVE EDGE-TRIGGERED FLIP-FLOP |

|

| 4 | SN54LS112A |

Texas Instruments |

Dual J-K Negative-Edge-Triggered Flip-Flops |

|

| 5 | SN54LS113A |

Motorola Inc |

DUAL JK NEGATIVE EDGE-TRIGGERED FLIP-FLOP |

|