Recherchez avec le numéro de pièce ainsi que le fabricant ou la description

IS61DDP2B21M36C1 |

| Part Number | IS61DDP2B21M36C1 |

| Manufacturer | ISSI |

| Description | 1Mx36 and 2Mx18 configuration available. Common I/O read and write ports. Max. 500 MHz clock for high bandwidth Synchronous pipeline read with self-timed late write operation. Double Data R... |

| Features |

DESCRIPTION

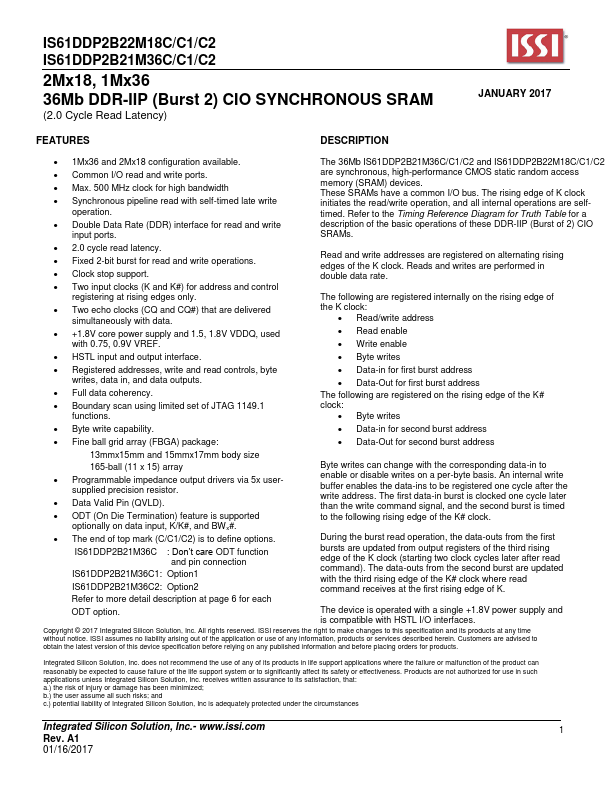

1Mx36 and 2Mx18 configuration available. Common I/O read and write ports. Max. 500 MHz clock for high bandwidth Synchronous pipeline read with self-timed late write operation. Double Data Rate (DDR) interface for read and write input ports. The 36Mb IS61DDP2B21M36C/C1/C2 and IS61DDP2B22M18C/C1/C2 are synchronous, high-performance CMOS static random access memory (SRAM) devices. These SRAMs have a common I/O bus. The rising edge of K clock initiates the read/write operation, and all internal operations are selftimed. Refer to the Timing Reference Diagram for Truth Table... |

| Document |

PDF 852.80KB |

| Distributor | Stock | Price | Buy |

|---|

| No. | Parte # | Fabricante | Descripción | Hoja de Datos |

|---|---|---|---|---|

| 1 | IS61DDP2B21M36C |

ISSI |

36Mb DDR-IIP CIO SYNCHRONOUS SRAM |

|

| 2 | IS61DDP2B21M36C2 |

ISSI |

36Mb DDR-IIP CIO SYNCHRONOUS SRAM |

|

| 3 | IS61DDP2B21M36A |

Integrated Silicon Solution |

36Mb DDR-IIP (Burst 2) CIO SYNCHRONOUS SRAM |

|

| 4 | IS61DDP2B21M36A1 |

Integrated Silicon Solution |

36Mb DDR-IIP (Burst 2) CIO SYNCHRONOUS SRAM |

|

| 5 | IS61DDP2B21M36A2 |

Integrated Silicon Solution |

36Mb DDR-IIP (Burst 2) CIO SYNCHRONOUS SRAM |

|