Recherchez avec le numéro de pièce ainsi que le fabricant ou la description

CY7C4021KV13 |

| Part Number | CY7C4021KV13 |

| Manufacturer | Cypress Semiconductor |

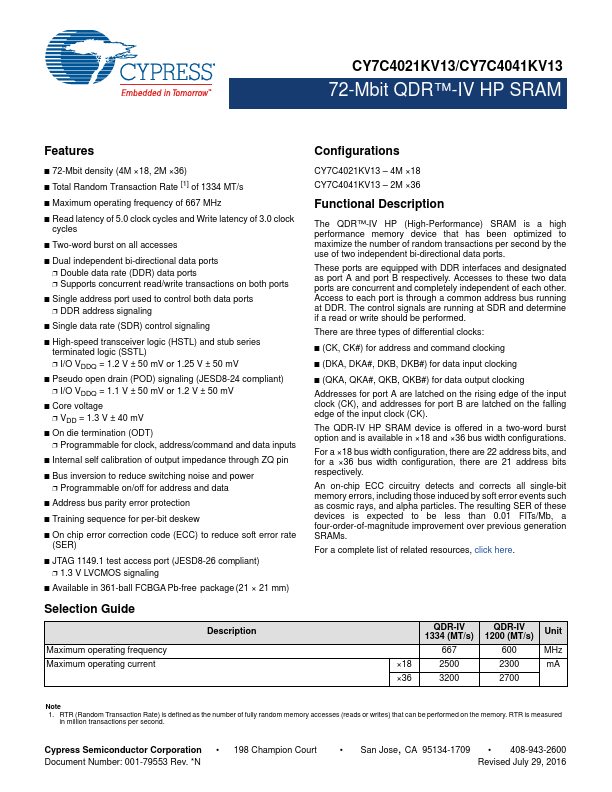

| Description | CY7C4021KV13/CY7C4041KV13 72-Mbit QDR™-IV HP SRAM 72-Mbit QDR™-IV HP SRAM Features ■ 72-Mbit density (4M ×18, 2M ×36) ■ Total Random Transaction Rate [1] of 1334 MT/s ■ Maximum operating frequency of... |

| Features |

■ 72-Mbit density (4M ×18, 2M ×36) ■ Total Random Transaction Rate [1] of 1334 MT/s ■ Maximum operating frequency of 667 MHz ■ Read latency of 5.0 clock cycles and Write latency of 3.0 clock cycles ■ Two-word burst on all accesses ■ Dual independent bi-directional data ports ❐ Double data rate (DDR) data ports ❐ Supports concurrent read/write transactions on both ports ■ Single address port used to control both data ports ❐ DDR address signaling ■ Single data rate (SDR) control signaling ■ High-speed transceiver logic (HSTL) and stub series terminated logic (SSTL) ❐ I/O VDDQ = 1.2 V ± 50 mV or... |

| Document |

PDF 1.72MB |

| Distributor | Stock | Price | Buy |

|---|

| No. | Partie # | Fabricant | Description | Fiche Technique |

|---|---|---|---|---|

| 1 | CY7C402 |

Cypress Semiconductor |

(CY7C401 - CY7C404) 64 x 4 Cascadable FIFO / 64 x 5 Cascadable FIFO |

|

| 2 | CY7C401 |

Cypress Semiconductor |

(CY7C401 - CY7C404) 64 x 4 Cascadable FIFO / 64 x 5 Cascadable FIFO |

|

| 3 | CY7C403 |

Cypress Semiconductor |

(CY7C401 - CY7C404) 64 x 4 Cascadable FIFO / 64 x 5 Cascadable FIFO |

|

| 4 | CY7C404 |

Cypress Semiconductor |

(CY7C401 - CY7C404) 64 x 4 Cascadable FIFO / 64 x 5 Cascadable FIFO |

|

| 5 | CY7C4041KV13 |

Cypress Semiconductor |

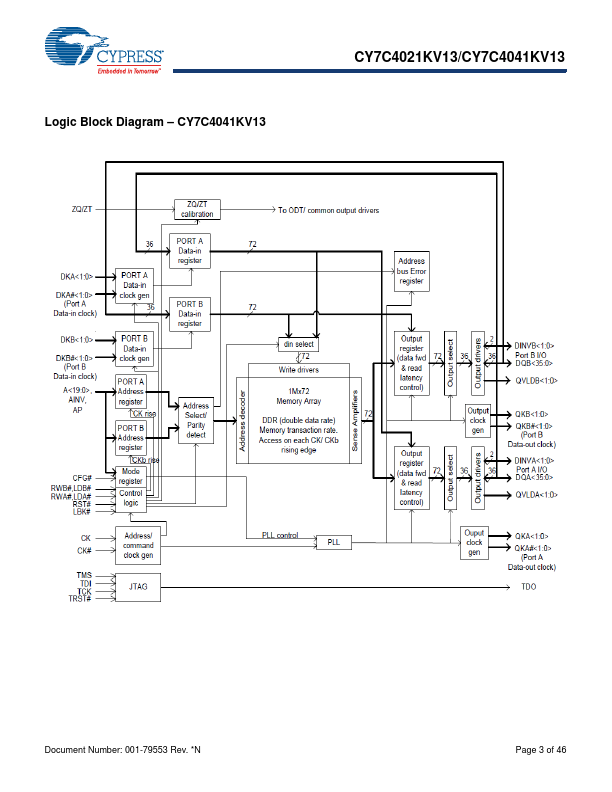

72-Mbit QDR-IV HP SRAM |

|