Recherchez avec le numéro de pièce ainsi que le fabricant ou la description

AS4C128M16D2A-25BCN |

| Part Number | AS4C128M16D2A-25BCN |

| Manufacturer | Alliance Semiconductor |

| Description | AS4C128M16D2A-25BCN AS4C128M16D2A-25BIN Revision History 2Gb AS4C128M16D2A - 84 ball FBGA PACKAGE Revision Details Rev 1.0 Preliminary datasheet Date Dec 2015 Alliance Memory Inc. 511 Taylor Way, S... |

| Features |

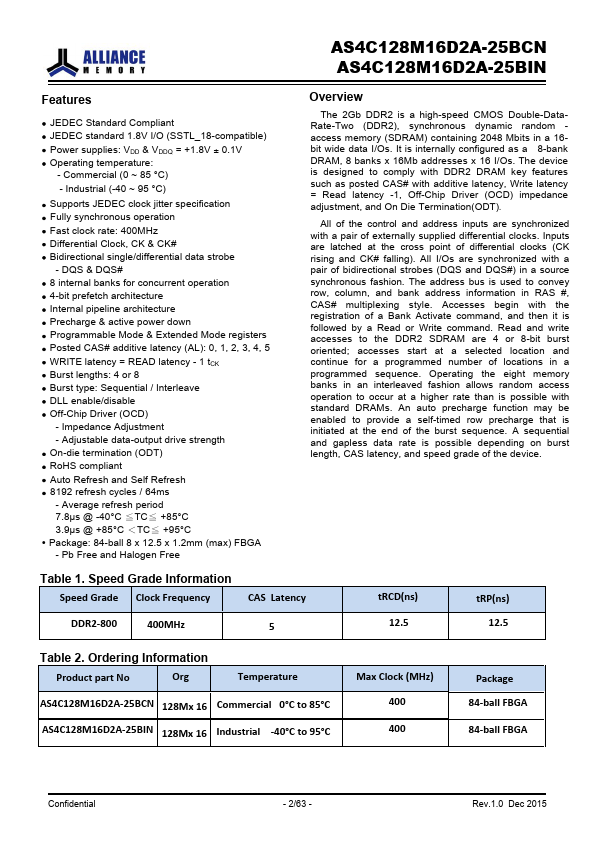

• JEDEC Standard Compliant • JEDEC standard 1.8V I/O (SSTL_18-compatible) • Power supplies: VDD & VDDQ = +1.8V ± 0.1V • Operating temperature: - Commercial (0 ~ 85 °C) - Industrial (-40 ~ 95 °C) • Supports JEDEC clock jitter specification • Fully synchronous operation • Fast clock rate: 400MHz • Differential Clock, CK & CK# • Bidirectional single/differential data strobe - DQS & DQS# • 8 internal banks for concurrent operation • 4-bit prefetch architecture • Internal pipeline architecture • Precharge & active power down ... |

| Document |

PDF 2.69MB |

| Distributor | Stock | Price | Buy |

|---|

| No. | Partie # | Fabricant | Description | Fiche Technique |

|---|---|---|---|---|

| 1 | AS4C128M16D2A-25BIN |

Alliance Semiconductor |

2Gb DDR2 |

|

| 2 | AS4C128M16D3A-12BIN |

Alliance Semiconductor |

2Gb Double-Data-Rate-3 DRAM |

|

| 3 | AS4C128M16D3B-12BCN |

Alliance Semiconductor |

Double-data-rate architecture |

|

| 4 | AS4C128M16D3LA-12BIN |

Alliance Semiconductor |

128M x 16 bit DDR3L Synchronous DRAM |

|

| 5 | AS4C128M16D3LB-12BCN |

Alliance Semiconductor |

Double-data-rate architecture |

|