Recherchez avec le numéro de pièce ainsi que le fabricant ou la description

GS81302TT110E |

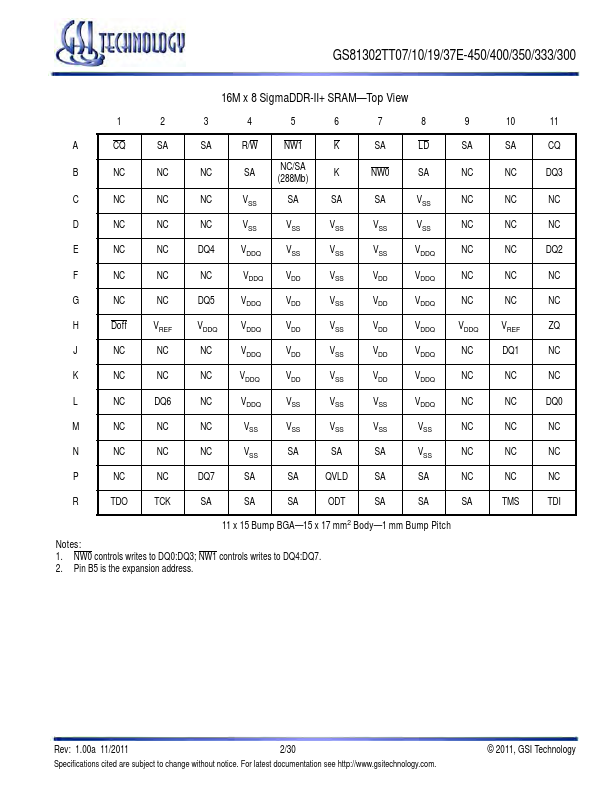

| Part Number | GS81302TT110E |

| Manufacturer | GSI Technology |

| Description | Table Symbol Description Type Comments SA Synchronous Address Inputs Input — R/W Synchronous Read Input High: Read Low: Write BW0–BW3 Synchronous Byte Writes Input Active Low LD Synchro... |

| Features |

• 2.0 Clock Latency • Simultaneous Read and Write SigmaDDR™ Interface • Common I/O bus • JEDEC-standard pinout and package • Double Data Rate interface • Byte Write controls sampled at data-in time • Burst of 2 Read and Write • Dual-Range On-Die Termination (ODT) on Data (D), Byte Write (BW), and Clock (K, K) inputs • 1.8 V +100/ –100 mV core power supply • 1.5 V or 1.8 V HSTL Interface • Pipelined read operation with self-timed Late Write • Fully coherent read and write pipelines • ZQ pin for programmable output drive strength • Data Valid pin (QVLD) Support • IEEE 1149.1 JTAG-compliant Bounda... |

| Document |

PDF 216.17KB |

| Distributor | Stock | Price | Buy |

|---|

| No. | Parte # | Fabricante | Descripción | Hoja de Datos |

|---|---|---|---|---|

| 1 | GS81302TT11E |

GSI Technology |

144Mb SigmaDDR-II+ Burst of 2 SRAM |

|

| 2 | GS81302TT11GE |

GSI Technology |

144Mb SigmaDDR-II+ Burst of 2 SRAM |

|

| 3 | GS81302TT107E |

GSI Technology |

144Mb SigmaDDR-II+ Burst of 2 SRAM |

|

| 4 | GS81302TT10E |

GSI Technology |

144Mb SigmaDDR-II+ Burst of 2 SRAM |

|

| 5 | GS81302TT10GE |

GSI Technology |

144Mb SigmaDDR-II+ Burst of 2 SRAM |

|