Recherchez avec le numéro de pièce ainsi que le fabricant ou la description

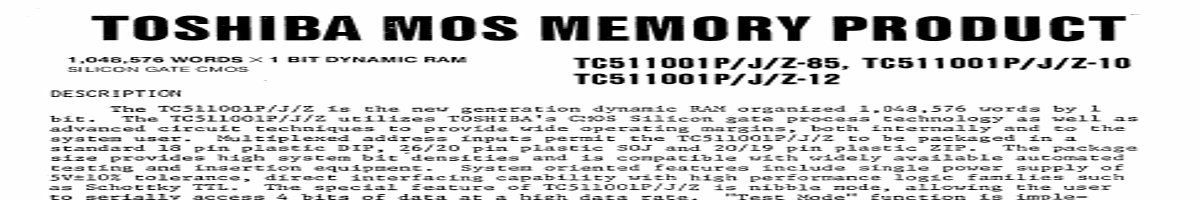

TC511001 P/J/Z-S5, TC511001 P/J/Z-l0 TC511 001 P/J/Z-12 The TC5ll00lP/J/Z is the new generation dynamic R&~ organized 1,048,576 ~vords by 1 bit. The TC5ll00lP/J/Z utilizes TOSHIBA's caos Silicon gate process technology as well as advanced circuit techniques to provide wide operating margins, both internally and to the system user. Multiplexed address input.

include single power supply of 5V±10% tolerance, direct interfacing capability with high performance logic families such as Schottky TTL. The special feature of TC5Il00IP/J/Z is nibble mode, allowing the user to serially access 4 bits of data at a high data r.

| No. | Partie # | Fabricant | Description | Fiche Technique |

|---|---|---|---|---|

| 1 | TC511001Z-10 |

Toshiba |

DRAM |

|

| 2 | TC511001Z-12 |

Toshiba |

DRAM |

|

| 3 | TC511001AJ-10 |

Toshiba |

DRAM |

|

| 4 | TC511001AJ-70 |

Toshiba |

DRAM |

|

| 5 | TC511001AJ-80 |

Toshiba |

DRAM |

|

| 6 | TC511001AP-10 |

Toshiba |

DRAM |

|

| 7 | TC511001AP-70 |

Toshiba |

DRAM |

|

| 8 | TC511001AP-80 |

Toshiba |

DRAM |

|

| 9 | TC511001AZ-10 |

Toshiba |

DRAM |

|

| 10 | TC511001AZ-70 |

Toshiba |

DRAM |

|

| 11 | TC511001AZ-80 |

Toshiba |

DRAM |

|

| 12 | TC511001J-10 |

Toshiba |

DRAM |

|