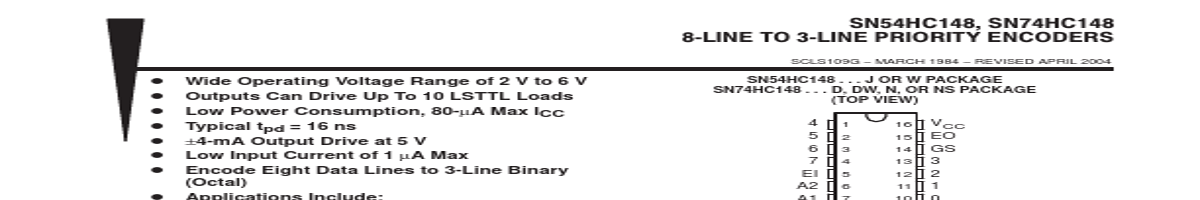

ordering information The ’HC148 devices feature priority decoding of the inputs to ensure that only the highest-order data line is encoded. These devices encode eight data lines to 3-line (4-2-1) binary (octal). Cascading circuitry (enable input EI and enable output EO) has been provided to allow octal expansion without the need for external circuitry. Data .

12 2 11 1 10 0 9 A0 SN54HC148 . . . FK PACKAGE (TOP VIEW) EO VCC NC 4 5 6 3 2 1 20 19 4 18 GS 75 17 3 NC 6 16 NC EI 7 15 2 A2 8 14 1 9 10 11 12 13 0 A0 NC GND A1 NC − No internal connection ORDERING INFORMATION TA PACKAGE† ORDERABLE PART NUMBER TOP-SIDE MARKING PDIP − N Tube of 25 SN74HC148N SN74HC148N Tube of 40 SN74HC148D −40°C to 85°C SOIC − D Reel of 2500 Reel of 250 SN74HC148DR SN74HC148DT HC148 SOIC − DW Reel of 2000 SN74HC148DWR HC148 SOP − NS Reel of 2000 SN74HC148NSR HC148 CDIP − J −55°C to 125°C CFP − W Tube of 25 Tube of 150 SNJ54HC.

| No. | Partie # | Fabricant | Description | Fiche Technique |

|---|---|---|---|---|

| 1 | SNJ54HC148FK |

Texas Instruments |

8-LINE TO 3-LINE PRIORITY ENCODERS |

|

| 2 | SNJ54HC148J |

Texas Instruments |

8-LINE TO 3-LINE PRIORITY ENCODERS |

|

| 3 | SNJ54HC14J |

Texas Instruments |

Hex Schmitt-Trigger Inverters |

|

| 4 | SNJ54HC14W |

Texas Instruments |

Hex Schmitt-Trigger Inverters |

|

| 5 | SNJ54HC109FK |

Texas Instruments |

DUAL J-K POSITIVE-EDGE-TRIGGERED FLIP-FLOPS |

|

| 6 | SNJ54HC109J |

Texas Instruments |

DUAL J-K POSITIVE-EDGE-TRIGGERED FLIP-FLOPS |

|

| 7 | SNJ54HC109W |

Texas Instruments |

DUAL J-K POSITIVE-EDGE-TRIGGERED FLIP-FLOPS |

|

| 8 | SNJ54HC10FK |

Texas Instruments |

TRIPLE 3-INPUT POSITIVE-NAND GATES |

|

| 9 | SNJ54HC10J |

Texas Instruments |

TRIPLE 3-INPUT POSITIVE-NAND GATES |

|

| 10 | SNJ54HC10W |

Texas Instruments |

TRIPLE 3-INPUT POSITIVE-NAND GATES |

|

| 11 | SNJ54HC112FK |

Texas Instruments |

DUAL J-K NEGATIVE-EDGE-TRIGGERED FLIP-FLOPS |

|

| 12 | SNJ54HC112J |

Texas Instruments |

DUAL J-K NEGATIVE-EDGE-TRIGGERED FLIP-FLOPS |

|