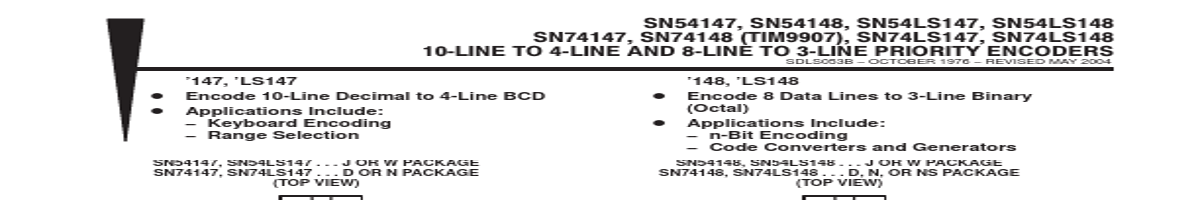

ordering information These TTL encoders feature priority decoding of the inputs to ensure that only the highest-order data line is encoded. The ’147 and ’LS147 devices encode nine data lines to four-line (8-4-2-1) BCD. The implied decimal zero condition requires no input condition, as zero is encoded when all nine data lines are at a high logic level. The ’1.

15 2 A2 8 14 1 9 10 11 12 13 B5 GND 4 NC NC A VCC 9 NC A1 5 GND 4 NC NC A0 VCC 0 E0 NC − No internal connection TYPE ’147 ’148 ’LS147 ’LS148 TYPICAL DATA DELAY 10 ns 10 ns 15 ns 15 ns TYPICAL POWER DISSIPATION 225 mW 190 mW 60 mW 60 mW NOTE: The SN54147, SN54LS147, SN54148, SN74147, SN74LS147, and SN74148 are obsolete and are no longer supplied. Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. PRODUCTION DATA.

| No. | Partie # | Fabricant | Description | Fiche Technique |

|---|---|---|---|---|

| 1 | SN5414 |

Texas Instruments |

Hex Schmitt-Trigger Inverters |

|

| 2 | SN54145 |

Texas Instruments |

BCD to Decimal Decoders/Drivers |

|

| 3 | SN54147 |

Texas Instruments |

10-LINE TO 4-LINE AND 8-LINE TO 3-LINE PRIORITY ENCODERS |

|

| 4 | SN5414J |

Texas Instruments |

Hex Schmitt-Trigger Inverter |

|

| 5 | SN5410 |

Texas Instruments |

TRIPLE 3-INPUT POSITIVE-NAND GATES |

|

| 6 | SN54107 |

Texas Instruments |

DUAL J-K FLIP-FLOPS |

|

| 7 | SN54109 |

Texas Instruments |

Dual J-K Positive-Edge-Triggered Flip-Flops |

|

| 8 | SN5412 |

Texas Instruments |

POSITIVE-NAND GATE |

|

| 9 | SN54121 |

Texas Instruments |

MONOSTABLE MULTIVIBRATORS |

|

| 10 | SN54122 |

Texas Instruments |

RETRIGGERABLE MONOSTABLE MULTIVIBRATORS |

|

| 11 | SN54123 |

Texas Instruments |

RETRIGGERABLE MONOSTABLE MULTIVIBRATORS |

|

| 12 | SN54125 |

Texas Instruments |

QUADRUPLE BUS BUFFERS |

|