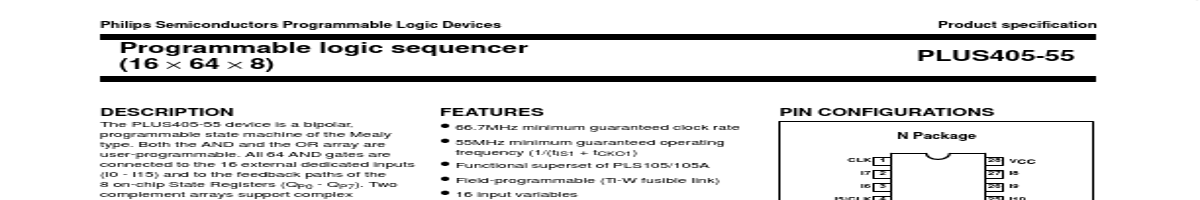

The PLUS405-55 device is a bipolar, programmable state machine of the Mealy type. Both the AND and the OR array are user-programmable. All 64 AND gates are connected to the 16 external dedicated inputs (I0 - I15) and to the feedback paths of the 8 on-chip State Registers (QP0 - QP7). Two complement arrays support complex IF-THEN-ELSE state transitions with a.

• 66.7MHz minimum guaranteed clock rate

• 55MHz minimum guaranteed operating

• Functional superset of PLS105/105A

• Field-programmable (Ti-W fusible link)

• 16 input variables

• 8 output functions

• 64 transition terms

• 8-bit State Register

• 8-bit Output Register

• 2 transition Complement Arrays

• Multiple clocks

• Programmable Asynchronous Initialization

• Power-on preset of all registers to “1”

• “On-chip” diagnostic test mode features for

• 950mW power dissipation (typ.)

• TTL compatible

• J-K or S-R flip-flop functions

• Automatic “Hold” states

• 3-State outputs

APPLICATIONS

access to s.

| No. | Partie # | Fabricant | Description | Fiche Technique |

|---|---|---|---|---|

| 1 | PLUS105-45 |

NXP |

Programmable logic sequencer |

|

| 2 | PLUS153B |

NXP |

Programmable logic arrays |

|

| 3 | PLUS153D |

NXP |

Programmable logic arrays |

|

| 4 | PLUS16L4D |

NXP |

PAL devices |

|

| 5 | PLUS16L6D |

NXP |

PAL devices |

|

| 6 | PLUS16L8D |

NXP |

PAL devices |

|

| 7 | PLUS16R4D |

NXP |

PAL devices |

|

| 8 | PLUS16R6D |

NXP |

PAL devices |

|

| 9 | PLUS16R8D |

NXP |

PAL devices |

|

| 10 | PLUS173-10 |

NXP |

Programmable logic array |

|

| 11 | PLU3 |

AMI |

CMOS Gate Array |

|

| 12 | PLUTO |

Mitel Networks |

Dual Mode CDMA/AMPS Baseband Interface |

|