The MT9045 T1/E1/OC3 System Synchronizer contains a digital phase-locked loop (DPLL), which provides timing and synchronization signals for multitrunk T1 and E1 primary rate transmission links and STS-3/OC3 links. The MT9045 generates ST-BUS clock and framing signals that are phase locked to either a 19.44 MHz, 2.048 MHz, 1.544 MHz, or 8 kHz input reference..

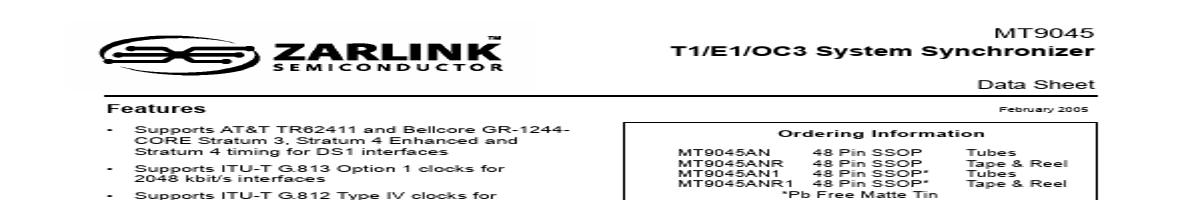

• Supports AT&T TR62411 and Bellcore GR-1244CORE Stratum 3, Stratum 4 Enhanced and Stratum 4 timing for DS1 interfaces

• Supports ITU-T G.813 Option 1 clocks for 2048 kbit/s interfaces

• Supports ITU-T G.812 Type IV clocks for 1,544 kbit/s interfaces and 2,048 kbit/s interfaces

• Supports ETSI ETS 300 011, TBR 4, TBR 12 and TBR 13 timing for E1 interfaces

• Selectable 19.44 MHz, 1.544 MHz, 2.048 MHz or 8kHz input reference signals

• Provides C1.5, C2, C4, C6, C8, C16, and C19 (STS-3/OC3 clock divided by 8) output clock signals

• Provides 5 styles of 8 KHz framing pulses

• Holdover frequency ac.

| No. | Partie # | Fabricant | Description | Fiche Technique |

|---|---|---|---|---|

| 1 | MT9040 |

Zarlink Semiconductor |

T1/E1 Synchronizer |

|

| 2 | MT9041 |

Mitel Networks Corporation |

Multiple Output Trunk PLL |

|

| 3 | MT9041B |

Mitel Networks Corporation |

T1/E1 System Synchronizer |

|

| 4 | MT9042 |

Mitel Networks Corporation |

Global Digital Trunk Synchronizer |

|

| 5 | MT9042C |

Mitel Networks Corporation |

Multitrunk System Synchronizer |

|

| 6 | MT9043 |

Zarlink Semiconductor |

T1/E1 System Synchronizer |

|

| 7 | MT9044 |

Mitel Networks Corporation |

T1/E1/OC3 System Synchronizer |

|

| 8 | MT9046 |

Zarlink Semiconductor |

T1/E1 System Synchronizer with Holdover |

|

| 9 | MT90 |

Techsem |

Thyristor Modules |

|

| 10 | MT900A-UR |

Marktech Corporate |

5mm Ultra Bright LED |

|

| 11 | MT90210 |

Mitel Networks Corporation |

Multi-Rate Parallel Access Circuit |

|

| 12 | MT90220 |

Mitel Networks Corporation |

Octal IMA/UNI PHY Device |

|