Ball Name Type CK_t, CK_c Input CKE Input CS_n CA[n:0] DQ[n:0] Input Input I/O DQS[n:0]_t, I/O DQS[n:0]_c DM[n:0] Input ODT Input M55D4G32128A (2R) Function Clock: CK_t and CK_c are differential clock inputs. All Double Data Rate (DDR) CA inputs are sampled on both positive and negative edge of CK_t. Single Data Rate (SDR) inputs, CS_n and CKE.

mpensated self refresh (ATCSR)

Auto refresh and self refresh

Refresh cycles: 8192 cycles/32ms

Average refresh period: 3.9μs

Partial-array self refresh (PASR)

Bank masking Segment masking

Deep power-down (DPD)

Programmable drive strength (DS)

On-die termination (ODT)

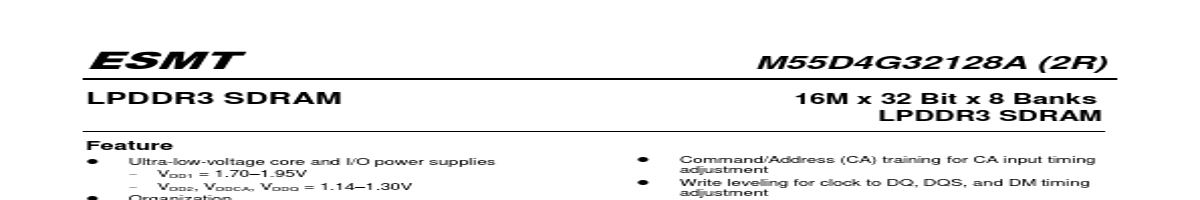

Ordering Information

Product ID

Max Freq. Data Rate RL

(MHz) (Mb/s/pin)

M55D4G32128A-GFBG2R

1066

2133

16

M55D4G32128A-EEBG2R

933

1866

14

M55D4G32128A-CDBG2R

800

1600

12

WL

VDD1 / VDD2, VDDCA, VDDQ

Package Comments

8

8

1.8V / 1.2V

178 ball BGA

Pb-free

6

Elite Semiconductor Microelectronics .

| No. | Partie # | Fabricant | Description | Fiche Technique |

|---|---|---|---|---|

| 1 | M55D4G32128A-CDBG2R |

ESMT |

16M x 32 Bit x 8 Banks LPDDR3 SDRAM |

|

| 2 | M55D4G32128A-GFBG2R |

ESMT |

16M x 32 Bit x 8 Banks LPDDR3 SDRAM |

|

| 3 | M5518 |

Edcon |

Rolling Ball Switch |

|

| 4 | M55302 |

BTC |

Pin Contacts |

|

| 5 | M55310 |

ETC |

OSCILLATOR |

|

| 6 | M55310 |

CTS |

Military Hybrid Clock Oscillators |

|

| 7 | M55310 |

Oscillatek |

Crystal Oscillators |

|

| 8 | M55342 |

Vishay Siliconix |

Qualified Thin Film Resistor |

|

| 9 | M5534206BE1C0RT0SV |

Vishay |

Qualified Thin Film Resistor |

|

| 10 | M55342K12B2B80R |

Vishay Siliconix |

QPL MIL-PRF-55342 Qualified Thin Film Resistor Chips |

|

| 11 | M55342M06B47K0RS6 |

Vishay Siliconix |

Thick Film Resistor Chips |

|

| 12 | M5576 |

MOJAY |

High performance current mode PWM controller |

|