The Intersil HCS125MS is a Radiation Hardened quad three-state buffer, each having its own output enable input. A high level on the enable input puts the output in a high impedance state. The HCS125MS utilizes advanced CMOS/SOS technology to achieve high-speed operation. This device is a member of radiation hardened, high-speed, CMOS/SOS Logic Family. The HC.

•

•

•

•

•

•

•

•

•

•

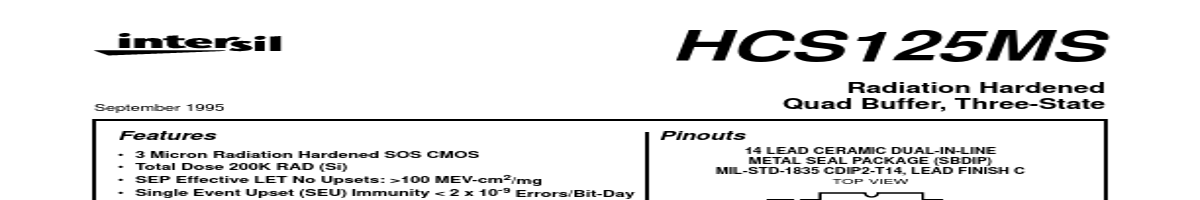

• 3 Micron Radiation Hardened SOS CMOS Total Dose 200K RAD (Si) SEP Effective LET No Upsets: >100 MEV-cm2/mg Single Event Upset (SEU) Immunity < 2 x 10-9 Errors/Bit-Day (Typ) Dose Rate Survivability: >1 x 1012 RAD (Si)/s Dose Rate Upset >1010 RAD (Si)/s, 20ns Pulse Latch-Up Free Under Any Conditions Military Temperature Range: -55oC to +125oC Significant Power Reduction Compared to LSTTL ICs DC Operating Voltage Range: 4.5V to 5.5V Input Logic Levels - VIL = 30% of VCC Max - VIH = 70% of VCC Min Input Current Levels Ii ≤ 5µA at VOL, VOH

•

Description

The Intersil HCS125MS .

| No. | Partie # | Fabricant | Description | Fiche Technique |

|---|---|---|---|---|

| 1 | HCS12 |

Motorola Inc |

USB2.0 to ATA/ATAPI Bridge |

|

| 2 | HCS1206 |

HITANO |

METAL STRIP CURRENT SENSING RESISTORS |

|

| 3 | HCS12H |

Freescale Semiconductor |

16-bit Microcontroller |

|

| 4 | HCS12NK65V |

SemiHow |

N-Channel MOSFET |

|

| 5 | HCS101 |

Microchip |

Fixed Code Encoder |

|

| 6 | HCS109MS |

Intersil |

Radiation Hardened Dual JK Flip Flop |

|

| 7 | HCS10MS |

Intersil |

Radiation Hardened Triple 3-Input NAND Gate |

|

| 8 | HCS112MS |

Intersil Corporation |

Radiation Hardened Dual JK Flip-Flop |

|

| 9 | HCS11MS |

Intersil |

Radiation Hardened Triple 3-Input AND Gate |

|

| 10 | HCS132MS |

Intersil |

Radiation Hardened Quad 2-Input NAND Schmitt Trigger |

|

| 11 | HCS138MS |

Intersil |

Radiation Hardened Inverting3-to-8 Line Decoder/Demultiplexer |

|

| 12 | HCS138T |

Intersil Corporation |

Radiation Hardened Inverting 3-to-8 Line Decoder/Demultiplexer |

|