Pin name A0 to A13 A10 (AP) BA0, BA1, BA2 DQ0 to DQ63 CB0 to CB7 /RAS /CAS /WE /CS0 CKE0 CK0 /CK0 DQS0 to DQS17, /DQS0 to /DQS17 SCL SDA SA0 to SA2 VDD VDDSPD VREF VSS ODT0 /RESET Par_In* 2 2 www.DataSheet4U.com Function Address input Row address Column address Auto precharge Bank select address Data input/output Check bit (Data input/output) Row address st.

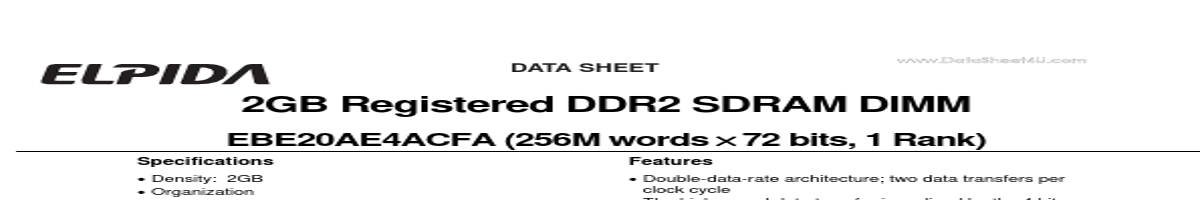

• Double-data-rate architecture; two data transfers per clock cycle

• The high-speed data transfer is realized by the 4 bits prefetch pipelined architecture

• Bi-directional differential data strobe (DQS and /DQS) is transmitted/received with data for capturing data at the receiver

• DQS is edge-aligned with data for READs; centeraligned with data for WRITEs

• Differential clock inputs (CK and /CK)

• DLL aligns DQ and DQS transitions with CK transitions

• Commands entered on each positive CK edge; data referenced to both edges of DQS

• Posted /CAS by programmable additive latency for better co.

| No. | Partie # | Fabricant | Description | Fiche Technique |

|---|---|---|---|---|

| 1 | EBE20AE4ACWA |

Elpida Memory |

2GB Registered DDR2 SDRAM DIMM |

|

| 2 | EBE20AE4ABFA |

Elpida Memory |

2GB Registered DDR2 SDRAM DIMM |

|

| 3 | EBE20RE4AAFA |

Elpida Memory |

2GB Registered DDR2 SDRAM DIMM |

|

| 4 | EBE20RE4ABFA |

Elpida Memory |

2GB Registered DDR2 SDRAM DIMM |

|

| 5 | EBE20RE4ACFA |

Elpida Memory |

2GB Registered DDR2 SDRAM DIMM |

|

| 6 | EBE21AD4AGFA |

Elpida Memory |

2GB Registered DDR2 SDRAM DIMM |

|

| 7 | EBE21AD4AGFB |

Elpida Memory |

2GB Registered DDR2 SDRAM DIMM |

|

| 8 | EBE21AD4AJFA |

Elpida Memory |

2GB Registered DDR2 SDRAM DIMM |

|

| 9 | EBE21AE8ACFA |

Elpida Memory |

2GB Registered DDR2 SDRAM DIMM |

|

| 10 | EBE21AE8ACWA |

Elpida Memory |

2GB Registered DDR2 SDRAM DIMM |

|

| 11 | EBE21EE8ABFA |

Elpida Memory |

2GB Unbuffered DDR2 SDRAM DIMM |

|

| 12 | EBE21EE8ACFA |

Elpida Memory |

2GB Unbuffered DDR2 SDRAM DIMM |

|