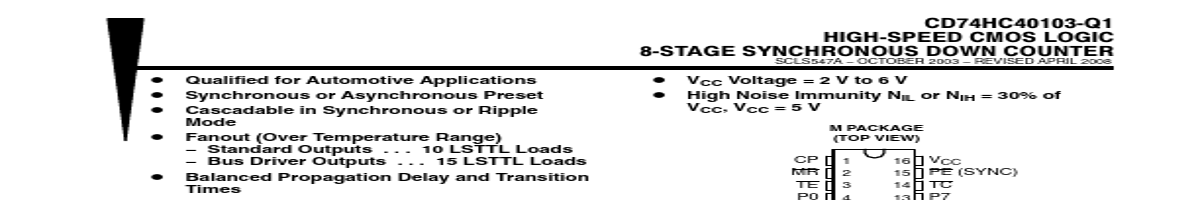

ordering information CD74HC40103-Q1 HIGH-SPEED CMOS LOGIC 8-STAGE SYNCHRONOUS DOWN COUNTER SCLS547A − OCTOBER 2003 − REVISED APRIL 2008 D VCC Voltage = 2 V to 6 V D High Noise Immunity NIL or NIH = 30% of VCC, VCC = 5 V M PACKAGE (TOP VIEW) CP MR TE P0 P1 P2 P3 GND 1 2 3 4 5 6 7 8 16 VCC 15 PE (SYNC) 14 TC 13 P7 12 P6 11 P5 10 P4 9 PL (ASYNC) The CD74HC.

isabling the clock, for clearing the counter to its maximum count, and for presetting the counter either synchronously or asynchronously. All control inputs and the terminal count (TC) output are active-low logic. In normal operation, the counter is decremented by one count on each positive transition of the clock (CP) output. Counting is inhibited when the terminal enable (TE) input is high. TC goes low when the count reaches zero, if TE is low, and remains low for one full clock period. When the synchronous preset enable (PE) input is low, data at the P0−P7 inputs are clocked into the counte.

| No. | Partie # | Fabricant | Description | Fiche Technique |

|---|---|---|---|---|

| 1 | CD74HC40103-EP |

Texas Instruments |

8-STAGE SYNCHRONOUS DOWN COUNTER |

|

| 2 | CD74HC40103 |

Texas Instruments |

8-Stage Synchronous Down Counters |

|

| 3 | CD74HC40105 |

Texas Instruments |

4-Bit x 16-Word FIFO Register |

|

| 4 | CD74HC4015 |

Texas Instruments |

Dual 4-Stage Static Shift Register |

|

| 5 | CD74HC4016 |

Texas Instruments |

Quad Bilateral Switch |

|

| 6 | CD74HC4017 |

Texas Instruments |

Decade Counter/Divider |

|

| 7 | CD74HC4017-EP |

Texas Instruments |

HIGH-SPEED CMOS LOGIC DECADE COUNTER/DIVIDER |

|

| 8 | CD74HC4017-Q1 |

Texas Instruments |

HIGH-SPEED CMOS LOGIC DECADE COUNTER/DIVIDER |

|

| 9 | CD74HC4002 |

Texas Instruments |

Dual 4-Input NOR Gate |

|

| 10 | CD74HC4020 |

Texas Instruments |

14-Stage Binary Counter |

|

| 11 | CD74HC4024 |

Texas Instruments |

7-Stage Binary Ripple Counter |

|

| 12 | CD74HC4040 |

Texas Instruments |

12-Stage Binary Counter |

|