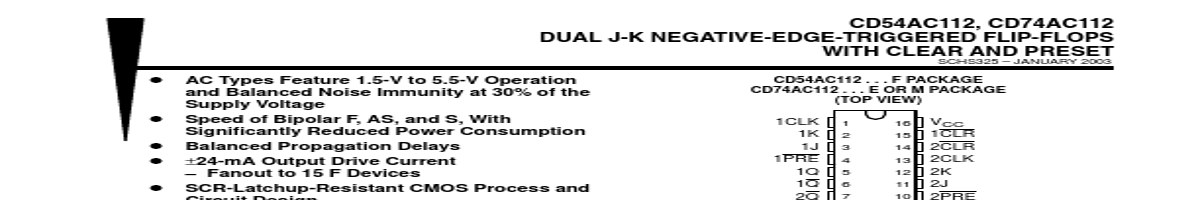

ordering information The ’AC112 devices contain two independent J-K negative-edge-triggered flip-flops. A low level at the preset (PRE) or clear (CLR) inputs sets or resets the outputs, regardless of the levels of the other inputs. When PRE and CLR are inactive (high), data at the J and K inputs meeting the setup-time requirements is transferred to the outpu.

rements is transferred to the outputs on the negative-going edge of the clock pulse (CLK). Clock triggering occurs at a voltage level and is not directly related to the fall time of the clock pulse. Following the hold-time interval, data at the J and K inputs may be changed without affecting the levels at the outputs. These versatile flip-flops can perform as toggle flip-flops by tying J and K high.

ORDERING INFORMATION

TA

PACKAGE†

ORDERABLE PART NUMBER

TOP-SIDE MARKING

PDIP

– E

Tube

CD74AC112E

CD74AC112E

–55°C to 125°C SOIC

– M

Tube

CD74AC112M

Tape and reel CD74AC112M96

AC112M

.

| No. | Partie # | Fabricant | Description | Fiche Technique |

|---|---|---|---|---|

| 1 | CD74AC10 |

Texas Instruments |

TRIPLE 3-INPUT POSITIVE-NAND GATES |

|

| 2 | CD74AC109 |

Texas Instruments |

DUAL J-K POSITIVE-EDGE-TRIGGERED FLIP-FLOPS |

|

| 3 | CD74AC138 |

Texas Instruments |

3-LINE TO 8-LINE DECODERS/DEMULTIPLEXERS |

|

| 4 | CD74AC139 |

Texas Instruments |

DUAL 2-LINE TO 4-LINE DECODERS/DEMULTIPLEXERS |

|

| 5 | CD74AC14 |

Texas Instruments |

Hex Schmitt-Trigger Inverter |

|

| 6 | CD74AC151 |

Texas Instruments |

8-LINE TO 1-LINE DATA SELECTOR/MULTIPLEXER |

|

| 7 | CD74AC153 |

Texas Instruments |

DUAL 4-LINE TO 1-LINE DATA SELECTORS/MULTIPLEXERS |

|

| 8 | CD74AC157 |

Texas Instruments |

QUADRUPLE 2-LINE TO 1-LINE DATA SELECTORS/MULTIPLEXERS |

|

| 9 | CD74AC158 |

Texas Instruments |

QUADRUPLE 2-LINE TO 1-LINE DATA SELECTOR/MULTIPLEXER |

|

| 10 | CD74AC161 |

Texas Instruments |

4-BIT SYNCHRONOUS BINARY COUNTERS |

|

| 11 | CD74AC163 |

Texas Instruments |

4-BIT SYNCHRONOUS BINARY COUNTERS |

|

| 12 | CD74AC164 |

Texas Instruments |

8-Bit Serial-In/Parallel-Out Shift Register |

|